Semiconductor Packaging 분석 시리즈

Highlights

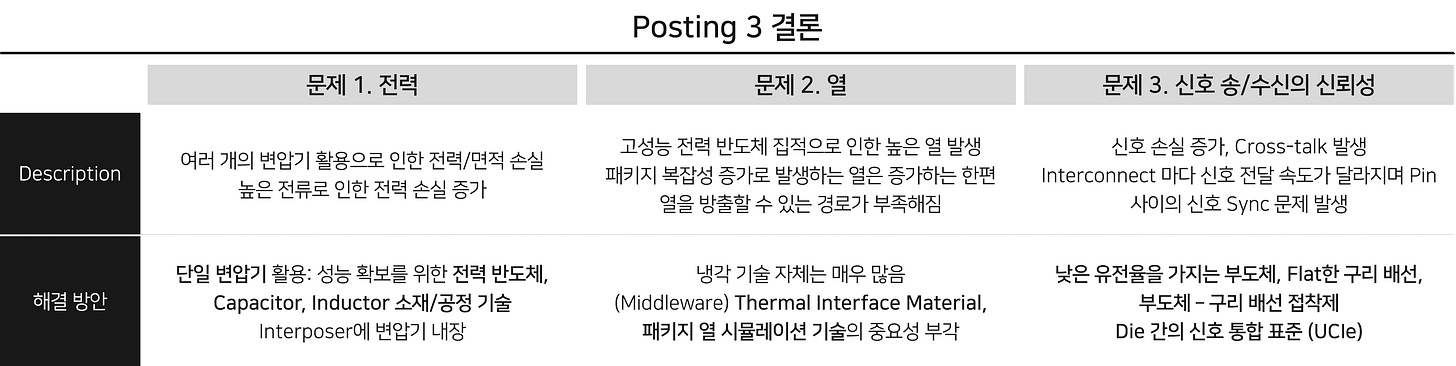

앞선 포스팅에서 패키지 기술의 큰 방향성은 (1) 하나의 패키지 안에 더 많은 Die를 올리는 것, (2) 그들의 효과적인 Computing을 위해 더 밀도 높은 Interconnect를 형성하는 것이라고 강조하였습니다. 이를 위한 기술 발전 과정에서 함께 해결해야만 하는 문제들이 여럿 있으며, 제 리서치에서 꼽은 가장 핵심적인 세 가지 문제는 다음과 같습니다:

Problem 1. 전력 공급

Problem 2. 열

Problem 3. 데이터 송/수신 과정의 신뢰성

이번 포스팅에서는 각 문제들이 왜 발생하게 되는지에 대해 설명하고, 이를 해결하기 위해 제안된 해결 방안들 역시 설명합니다. 결론적으로 GaN 기반의 전력 반도체의 Package Integration, 새로운 캐퍼시터(유전체)와 인덕터(자성) 소재, Thermal Interface Material의 필요성이 부각됩니다.

Problem 1. 전력 공급

하나의 패키지에서 여러 개의 Die가 작동하게 되면서, 아래 그림의 설명과 같은 기존의 전력 공급 시스템의 단점이 부각되기 시작합니다:

기존 전력 공급 시스템에서는 두 개의 Voltage Regulator(VR)가 활용됩니다. 패키지 외부로부터 48V의 전력이 공급되고, Substrate에 위치한 첫 번째 VR에서 이를 12V로 변환합니다. 12V로 변환된 전력은 Interposer에 위치한 두 번째 VR로 전달되고, 두 번째 VR은 12V의 전력을 1V의 전력으로 변환합니다. 1V로 변환된 전력은 다시 Interposer를 통과해 각각의 Die로 전달됩니다.

이 시스템의 한계점은 다음과 같습니다:

(붉은 상자 ①) VR은 필연적인 전력 손실을 수반합니다. 따라서 두 개의 VR을 활용하는 것은 당연하게도 더 큰 전력 손실을 발생시킵니다.

(붉은 상자 ①) 동일한 기능을 하는 두 개의 VR을 패키지 위에 올리기 때문에 면적 손실이 발생합니다. 집적화가 주요 과제인 현 상황에서 중복된 회로를 올리는 것은 비효율입니다.

(푸른 상자 ②) 같은 전력을 공급할 때 전류가 높으면 (=전압이 낮으면) 전력 손실이 증가합니다. 이런 이유 때문에 도시 등의 전력망은 고전압 송전선을 활용합니다. 실제로 전력 손실량은 전류의 제곱에 비례하여 증가하게 됩니다. 패키지 위에 1개의 Die가 있을 때보다 위 그림의 경우 Die가 5개이므로, 전류가 5배 증가하며 무려 25배의 전력 손실이 발생하게 됩니다. 따라서 이를 최소화하기 위해 낮은 전압에서의 전류 이동을 최소화해야 합니다.

이를 해결하고자 현재 제안되고 있는 시스템은 아래와 같은 구조를 가집니다.

두 개로 나뉘어져 있던 VR을 한 개로 통합합니다. 이에 따라 두 개의 VR로 인한 전력/면적 손실, 낮은 전압의 전류 전달로 인한 전력 손실로 대표되는 기존의 문제점을 ‘이론적으로’ 해결할 수 있습니다.

하지만 이러한 ‘이론적’인 관점에서의 장점을 활용하기 위해서는 다음과 같은 새로운 기술이 필요합니다:

전력 반도체

48V → 1V의 변환은 기존 구조의 변환과 비교해 훨씬 큰 폭의 변압을 수반하고, 더하여 낮은 전압으로 변환하는 저전압 작동을 수반합니다. 현재 활용되고 있는 실리콘 기반의 PowerFET는 이러한 변환 과정에서 큰 손실이 발생합니다. 이 변환 과정을 최소한의 에너지 손실로 수행할 수 있는 전력 반도체 소재로 GaN이 언급되고 있습니다.

Capacitor, Inductor 소재

VR은 전력 반도체, Capacitor, Inductor를 포함한 회로로 구성됩니다. VR의 스펙이 변화하려면 Capacitor와 Inductor의 성능도 함께 발맞추어 발전해야 합니다. Capacitor 높은 유전율을 갖춘 소재, Inductor에는 신뢰성 있는 자성을 갖춘 소재를 필요로 하고 있으나, 지금까지 개발된 소재들은 이를 만족하지 못하는 실정입니다.

단순한 물성 만족에 더해, 실제로 패키지에 적은 비용으로 실장할 수 있는 공정 적합성까지 확보해야 합니다. 2020년 Georgia Tech에서 수행한 Inductor 소재에 관한 연구가 좋은 템플릿이 됩니다. 이 연구에서는 소재 합성과 패키지 Integration에 대한 내용까지 다루고 있습니다.

Decoupling Capacitor 소재/공정

전력 전달 과정에서 발생할 수 있는 전류 Spike로 인한 손실, power quality 감소를 최소화하기 위해 각 Die와 가까운 영역에 decoupling capacitor를 추가합니다.

기존에 대표적으로 활용했던 것이 MLCC (Multi-layer Ceramic Capacitor)입니다. MLCC는 크기가 크기 때문에 패키지 바깥에 실장하게 됩니다. 이처럼 MLCC는 집적화 한계가 분명하기 때문에 새로운 소재와 integration 기술이 필요합니다.

현재는 Interposer에 Deep trench capacitor(DTC)를 형성하는 방법이 중요하게 제안되고 있으며, 이는 앞선 포스팅의 Interposer requirement에도 간단히 언급되어 있습니다 (’24년 MIM Capacitor). 2019년 TSMC가 그들의 CoWoS (Chip on Wafer on Substrate) 기술에 DTC를 도입하는 연구를 발표한 만큼, DTC는 짧은 시일 내에 패키징 기술의 중요 꼭지로 언급될 가능성이 높습니다.

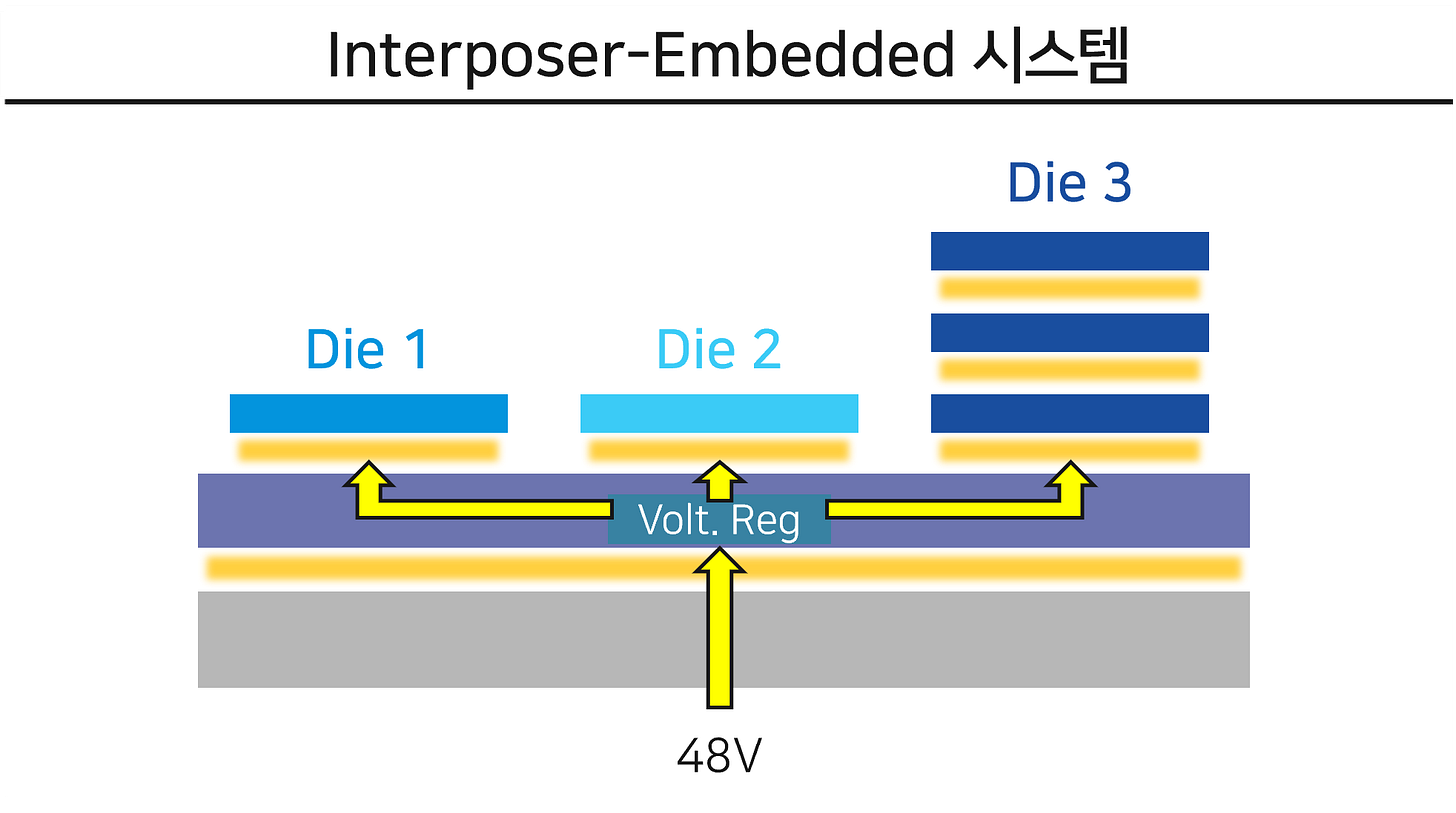

현안 과제를 해결한 다음 스텝으로 언급되는 방식은 아예 Interposer 안에 VR을 삽입하는 형태입니다.

위 그림과 같이 VR을 위한 별도의 면적이 필요하지 않음과 동시에 전류가 흐르는 경로의 길이를 최소화할 수 있어 가장 이상적인 형태의 전력 공급 기술이라고 할 수 있습니다.

이처럼 Interposer가 단순히 정보 전달의 통로 역할을 하는 것이 아니라 별도의 기능을 하는 경우 이를 ‘Active Interposer’라고 부릅니다.

관련해 잘 정리해둔 리뷰 논문과 최신 연구 논문을 공유합니다. (놀랍게도 두 논문 모두 프랑스의 CEA Leti 연구소에서 발표했습니다. 이전 포스팅의 Coolcube 기술 역시 CEA Leti의 작품이었죠. 이 연구소의 연구 흐름을 살펴보는 것도 유의한 스터디가 될 수 있겠습니다.)

정리하자면, 전력 공급 문제를 해결하기 위한 주요 기술 길목은 아래와 같습니다:

중단기적 관점에서 중요한 기술

고효율 48V → 1V 변환이 가능한 전력 반도체

고유전율의 Capacitor 소재와 Integration 기술

높은 자성을 가지는 Inductor 소재와 Integration 기술

장기적 관점에서 중요한 기술

Interposer에 시스템을 내장하는 기술 (Active Interposer)

Problem 2. 열

Dennard Scaling이 깨지면서 하나의 Die에서 필요로 하는 전력의 양이 증가했습니다. 전력을 많이 쓰면 동시에 열도 더 많이 발생하게 됩니다. 여러 개의 Die를 Integration하는 패키지에서는 이전에 다루지 않았던 규모의 열이 발생하기 시작합니다. 단순한 Die 개수 증가에 따른 변화가 끝이 아닙니다. 패키지의 복잡성이 증가하며 아래 그림에서 설명하는 새로운 문제점들이 점화되기 시작합니다:

Voltage Regulator

기존 대비해서 훨씬 더 큰 폭의 전압 변환 성능을 필요로 합니다. 이전에는 여러 개의 VR을 활용했기 때문에 발생하는 열이 공간적으로 분리되어 있었는데요. 이제는 하나의 VR이 발생하는 모든 열을 감당해야 하는 상황으로 변하게 됩니다.

Interconnect 밀도 증가

Interconnect는 여러 계면과 상호작용하기 때문에 전기 저항 손실, 유전 손실 등 다양한 손실 메커니즘이 발생하고, 이에 따른 열 발생량도 적지 않습니다.

현재의 선폭/간격이 약 30μm 수준이라고 어림잡고, 목표하는 1μm 수준까지 감소하게 된다고 생각해보겠습니다. 단순히 Interconnect 숫자만 고려할 때, 발생하는 열은 지금의 900배로 증가합니다.

3D Stacking

수직 방향의 적층이 증가하는 추세입니다. HBM4는 12개 혹은 16개의 Die가 적층된 구조입니다. Die 개수 증가, Interconnect 증가로 인한 열 발생 증가는 필연적입니다.

심각한 문제는 가장 아래에 위치한 Die가 열을 배출할 길이 없다는 점입니다. 심지어 가장 아래층 Die는 프로세서와 소통하고 위층 Die를 제어하는 역할까지 담당하는 등 3D Stack 전체에서 가장 중요한 Die라고 보아도 무방합니다. 열이 방출되지 않아 야기되는 최하층 Die의 성능 저하는 3D Stack 전체의 성능을 저하시킬 가능성이 높습니다.

이러한 문제를 해결하기 위해 패키지 내부 구조 변화부터 시작해, 패키지 수준과 시스템 수준에서의 Cooling system이 제안되기 시작합니다. 개인적으로 공부 과정 중에 가장 답답한 기술이 바로 열 관리 기술인데요. 제안되는 방법이 너무 많아서 도무지 어떤 방법이 바이블인지 아직 잘 모르겠습니다. 앞선 섹션에서 살펴보았던 전력 공급 문제의 경우, 전압 범위와 변환 성능을 고려하면 GaN라는 소재가 딱 떨어지는데, 열 관리 솔루션은 여전히 오리무중인 서술형 답안지 느낌입니다.

그런 와중에 금광 속 청바지 같은 역할을 하는 존재가 있었으니 첫째는 Thermal Interface Material (TIM)입니다. TIM의 경우 이전 배터리 열 관리 시스템 포스팅에서 다룬 ‘방열 소재’와 일맥상통합니다. SK 하이닉스의 MR-MUF 기술 역시 TIM과 연결지점을 가진다고 볼 수 있겠습니다. 어떤 냉각 시스템을 사용한다고 해도, 그 냉각 시스템까지 빠르게 열을 가져가야 유의미한 결과를 얻을 수 있습니다. 따라서 어떤 시스템 기술이 채택된다 하더라도 TIM은 그 중요성이 지속해서 강조될 것이라고 생각합니다.

둘째는 시뮬레이션 기술입니다. 개인적으로 패키지 내부의 열 시뮬레이션에는 기술적인 관심을 가지고 있는 만큼, 관련해서 (기술 몰빵) 포스팅을 추후 진행하도록 하겠습니다.

분명 더 깊이 공부하다 보면 중요한 트렌드를 찾을 수 있을 것이라고 생각합니다. 위 두 가지 내용을 포함한 열 관리 기술에 대한 내용은 다가오는 포스팅에서 보다 상세히 다루어보도록 하겠습니다.

Problem 3. 신호 송/수신 과정의 신뢰성

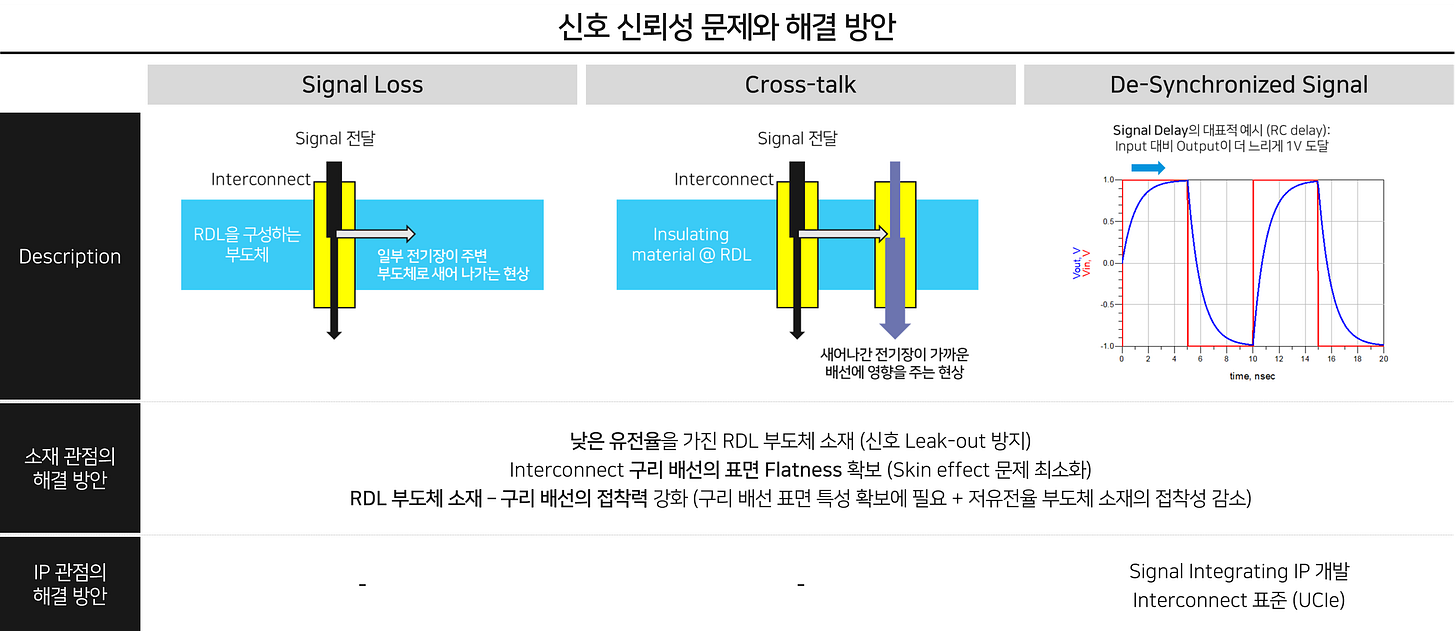

Interconnect 미세화로 신호 송/수신의 절대적인 양이 증가하고, 하나의 Interconnect에서 더 잦은 송/수신이 이루어지면서 다양한 문제가 발생합니다. 아래 그림에서 상세한 내용을 설명합니다:

Signal Loss

금속 구리 배선 Interconnect에서 이를 감싸고 있는 부도체로 신호가 새어 나가는 현상을 의미합니다. Signal loss는 Interconnect 송/수신 빈도에 비례하여 증가합니다.

Cross-talk

손실된 신호가 이웃한 Interconnect에 가서 참견하는 현상입니다. 손실되는 신호의 크기는 점점 커지고, Interconnect 사이의 간격이 줄어들면서 Cross-talk 문제가 대두됩니다.

De-synchronized Signal

금속 Interconnect 자체가 저항(Resistor)으로 작용하고, Interconnect와 부도체 사이의 의도하지 않은 공극이나 부도체 자체가 캐퍼시터(Capacitor)로 작용하면서 신호 전달 과정에서 RC delay가 발생하게 됩니다. RC delay 자체는 신호의 전달 속도를 늦추는 역할을 하기 때문에 높은 주파수 작동을 방해하는 요인으로 작용합니다.

모든 Interconnect에서 저항값과 캐퍼시터 값이 제각각이라는 점에 주목해야 합니다. 수만 개의 Interconnect가 동시에 신호를 전달하는데 신호가 도달하는 시간이 전부 달라질 수 있다는 것입니다. 이를 ‘Signal Integrity Loss’라고 이야기합니다. Die와 Interconnect 수가 증가하는 현 상황에서 중요하게 다루어져야 할 문제입니다.

놀랍게도, 이 모든 문제를 해결할 수 있는 해결 방안이 존재합니다.

유전율이 낮은 부도체의 적용 (low Dk material)

신호 손실은 유전율이 높을수록 많이 발생하며, 유출된 신호는 유전율이 높을수록 쉽게 이웃한 Interconnect로 전달됩니다. RC delay 역시 유전율이 높을수록 심화됩니다. 따라서, 유전율이 낮은 부도체를 활용하는 하나의 방법으로 신호 손실, Cross-talk, Signal Integrity 문제를 동시에 해결할 수 있게 됩니다.

구리 배선의 표면 Flatness 확보

구리 배선의 표면이 울퉁불퉁해지면, 전류는 표면을 따라 흐른다는 Skin effect에 의해 신호 전달 경로 증가, RC delay 심화, Dielectric loss 심화 등 다양한 문제가 파생됩니다. 위에 언급한 모든 문제의 원인들입니다. 특히나 주파수가 증가할 수록 Skin effect에 의한 영향력은 증가하므로 표면이 Flat한 구리 배선을 만드는 것은 아주 중요한 과제가 됩니다.

부도체 소재 - 구리 배선의 접착력 강화

구리 배선이 울퉁불퉁한 이유는 접착력을 강화하기 위해서입니다. Flat한 배선에서도 배선 탈락이 생기지 않도록 뛰어난 접착력을 가진 소재가 필요합니다.

더하여 현재 제안되고 있는 유전율이 낮은 부도체는 주로 불소를 함유하고 있으며, 이 경우 구리와의 접착력은 더욱 감소하는 것으로 알려져 있습니다.

여기에 더해, 신호 전달을 조정하는 IP가 중요하게 언급될 가능성이 있습니다. 특히나 여러 개의 다른 회사에서 만들어진 Chiplet을 연결하는 과정에서 신호 전달을 조정해야 하기 때문에 성능을 담보할 수 있는 표준이 필요합니다. 현재는 Universal Chiplet Interconnect Express (UCIe) 표준을 주목해야 할 것으로 보이며, Intel, 삼성, Arm, Qualcomm, TSMC, NVIDIA 등 주요 기업들이 참여하고 있습니다. 표준과 별개로 신호 전달 조정을 위한 IP는 각 Fabless에서 직접 개발하는 것으로 파악됩니다. 향후 다양한 Die에서 전달되는 신호를 통합하는 데 있어 강력한 성능을 지닌 IP를 개발하는 기업에 유의한 투자 기회가 있을 것이라고 생각됩니다.

정리하자면, 신호 송/수신 신뢰성 문제를 해결하기 위한 주요 기술 길목은 아래와 같습니다:

중단기적 관점에서 중요한 기술

유전율이 낮은 부도체 기술

Flat한 구리 배선

부도체 - 배선 접착 소재

장기적 관점에서 중요한 기술

여러 회사의 Die에서 전달되는 신호를 통합하는 표준

표준에 기반한 강력한 성능의 신호 전달 IP

결론

패키징에서 이외 다른 영역으로 기술 내용이 확장되니 생각보다 커버하기 쉽지 않네요. 다음 포스팅에서는 지금까지 다루었던 내용들을 한 번 정리해서 ‘꼭 해결해야 하는 문제’를 정리합니다. 놀랍게도 본 게임은 지금부터입니다. 각각의 중요 꼭지에서 실질적으로 어떤 변화가 일어나고 있는지 살펴보아야 합니다. 3월이 지나기 전에 좋은 기업들까지 소개할 수 있도록 열심히 공부하고 있으니, 계속해서 지켜봐주시면 감사하겠습니다. 오늘도 긴 글 읽어주셔서 감사합니다.