Semiconductor Packaging 분석 시리즈

Highlights

반도체 Packaging의 핵심 현안은 다음과 같음:

Package 하나에 더 많은 Die를 넣기 위해 기판 면적을 늘리고, 3D Stack 강화

Die들의 효과적인 Computing을 위해 Die-Die를 연결하는 Interconnect의 개수 확대 (=미세화)

이번 포스팅에서는 미세화 과정에 대해 상세히 다룸. 미세화 과정에는 다양한 기술적 변화가 필요하므로 기존에 주목받지 않던 player에게 새로운 기회가 있을 것으로 기대.

미세화 과정에서의 기술 변화 흐름은 다음 세 가지로 정리됨:

Interface Bonding 미세화: Cu-Cu Hybrid bonding의 본격화 + 특허 이슈 확인 필요

Interposer RDL/TSV 미세화: 기존 Interposer 제조 업체의 생산 능력 강화 예상

Packaging Substrate (Carrier) 미세화: Glass 기판 및 Glass 공정 유관 소재 업체에 새로운 기회가 생길 것 + 광통신 기술이 데이터 센터 운영의 패러다임을 바꿀 것

안녕하세요, 구독자 여러분. WAGU입니다. 지난 포스팅에서는 지금까지 반도체 Packaging이 어떤 이유로, 어떻게 발전해왔는지 전체적인 흐름을 살펴보았습니다. 이번 포스팅에서는 앞으로는 어떤 변화의 driver가 있고, 이를 충족하기 위해 어떤 기술이 함께 준비되어야 하는지 살펴보도록 하겠습니다. 다음 포스팅까지는 향후 패키징 산업의 ‘주요 쟁점을 찾아간다’는 것에 초점을 맞추고 있습니다. 투자의 관점에서 ‘어떤 기업에 투자해야 한다’는 내용과는 사뭇 다른 내용임을 강조합니다. 얼른 공부해서 좋은 기업들도 소개하도록 하겠습니다. 이번 포스팅도 재미있게 읽어주시면 감사하겠습니다.

반도체 Packaging 발전의 중심을 꿰뚫는 질문은 과장을 보태 딱 두 가지 뿐입니다.

하나의 Package에 더 많은 Die를 올리려면 어떻게 해야 할까?

그 많은 Die들이 더 효과적으로 Computing하려면 어떻게 해야 할까?

사실상 위의 두 가지 질문을 해결하기 위해 열 관리, 전력 공급, 신호 전달 등의 파생적인 질문이 던져지는 것일 뿐입니다.

첫 번째 질문에 대한 답변은 아주 간단히, 아래 두 개의 답변으로 정리될 수 있습니다.

Package의 면적을 늘린다. = 더 큰 Interposer, Substrate를 만든다.

Die를 위로 쌓는다. = 3D Stacking

이번 포스팅에서는 첫 번째 질문에 대한 상세한 분석은 진행하지 않습니다. (논리적으로 왜 두 번째 질문을 먼저 살펴보아야 하는지 1시간 째 적고 지우기를 반복했고, 설명에 실패했습니다. 관련해서 아직 잘 모르는 것 같습니다. 열심히 준비해서 첫 번째 질문에 대한 내용도 공유하겠습니다.)

두 번째 질문에 대한 답변은 더 간단합니다.

Die-Die를 연결하는 Interconnection의 수를 늘린다.

Die는 어차피 이미 설계되어서 나오기 때문에 Packaging 과정에서 성능을 바꿀 수는 없습니다. 따라서 Packaging에서 변화를 줄 수 있는 부분은 Interconnection의 수를 늘리는 부분입니다. Interconnection의 수를 늘리려면 전선을 더 가늘게 만들고 촘촘하게 배치해야 합니다.

즉, 미세화된 공정이 필요해집니다.

이번 포스팅에서는 어떤 부분에서 미세화가 필요한지, 그리고 이를 구현하기 위해서 어떤 세부적인 기술이 필요한지 살펴봅니다.

State-of-the-Art (SOTA) 패키지 구조와 발전 방향

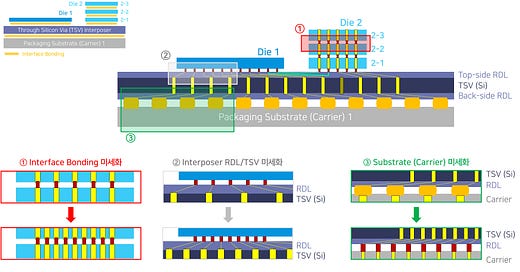

지난 포스팅의 마무리 단계에서 현재의 가장 발전된 패키지 구조는 3D Stack on 2.5D Packaging이라고 언급한 바 있습니다. 이 구조를 좀 더 상세히 살펴보면 아래 그림과 같습니다.

Die / TSV Interposer 사이의 Interface bonding은 빨간색 기둥으로 표시되어 있습니다. Die 2-1 / Die 2-2 사이의 간격도 마찬가지입니다. 빨간색 기둥은 크기가 작고 간격이 촘촘합니다. 앞으로 우리는 크기 대신 ‘선폭’이라는 단어를 쓰겠습니다. 즉, 빨간색 기둥은 선폭/간격이 작습니다.

TSV Interposer / Packaging Substrate 사이의 Interface bonding은 주황색 동그라미로 표시되어 있습니다. 상대적으로 크기도 크고 간격도 넓습니다. 즉, 주황색 동그라미는 선폭/간격이 큽니다.

Bonding과 TSV 사이에는 Redistribution Layer (RDL)이라는 얇은 층이 있습니다. 그림에서는 표현하지 않았지만 Bonding과 Die 사이에도 RDL이 필요합니다. Die와 TSV 사이의 배선이 공간적으로 동일하게 배치되지 않기 때문에, 이를 재배치(Redistribution)하는 기능을 삽입한 것입니다. 이는 TSV와 Packaging Substrate 사이에도 필요합니다. 예상컨데, Bonding이 촘촘할수록 RDL의 선폭/간격이 작아져야 할 것으로 보입니다.

더 많은 Interconnection을 만들기 위해 크게 세 가지 관점에서 기술의 발전이 필요합니다.

Interface bonding 미세화 (위 그림의 붉은 상자)

Interconnection의 밀도를 높이기 위해 가장 먼저 선행되어야 하는 기술입니다. Interface bonding을 통해 연결되는 pin의 수가 많아지면 한번에 더 많은 정보를 전달할 수 있게 됩니다. 우리가 잘 알고 있는 High Bandwidth Memory (HBM) 역시 이 Bonding pin 숫자를 늘려 더 높은 Bandwidth를 구현합니다.

Interposer RDL/TSV 미세화 (위 그림의 회색 상자)

Bonding이 촘촘해지면, 각 Bonding 지점과 연결되는 RDL의 배선도 함께 촘촘해져야 합니다. RDL 배선이 많아졌는데 여기에 연결될 Through Silicon Via (TSV)가 없으면, 새로 생긴 RDL 배선은 더 이상 정보를 전달할 수 없게 됩니다. 따라서 미세화된 Interface bonding의 스펙을 맞추기 위해 RDL과 TSV도 함께 미세화되어야 합니다.

Substrate (Carrier) 미세화

RDL/TSV가 미세화되어야 하는 이유와 동일합니다. TSV 숫자가 많아져서 밖으로 전달할 수 있는 정보의 양이 아무리 많아진다고 해도, 이를 전달받을 수 있는 기판 배선도 필요합니다. 기판의 배선이 촘촘해지지 않으면 이 구간에서 병목 현상이 생기거나, 혹은 더 넓은 기판이 필요해집니다. 이를 위해 업계는 유리 소재를 활용하는 것을 제안합니다. 기판 배선의 미세화를 구현하기 어렵다면, 이전 포스팅에서 언급한 바와 같이 Redunancy를 최소화하기 위해 2.1D 패키지 기술을 활용하게 됩니다.

지금부터 각각을 실제로 구현하기 위해 구체적으로 어떤 기술이 필요한지 살펴보도록 하겠습니다.

1. Interface Bonding 미세화

위에서 언급한 바와 같이 Interface Bonding을 미세화하는 것이 전체 패키지 미세화의 신호탄입니다. 이번 섹션에서는 Interface Bonding 기술에 대한 개괄적인 내용을 살펴보고, 앞으로의 주요 쟁점을 짚습니다.

1~2세대 Interface Bonding = Solder의 활용

앞선 2.5D 그림에서 보았던 커다란 주황색 동그라미는 ‘솔더 볼’이라는 1세대 기술을 뜻하고, 빨간색 기둥은 마이크로범프라는 2세대 기술을 뜻합니다.

1세대 기술은 일정 수준 이상의 미세한 선폭/간격을 만들어낼 수 없습니다. 하지만 여전히 Interposer와 Substrate 사이의 Bonding은 1세대 기술을 사용하고 있습니다. 2세대 기술이 이미 성숙한 상황에도 아직까지 1세대 기술을 활용하는 이유는 기판의 선폭/간격이 마이크로범프의 선폭/간격에 대응할 수 있을 만큼 미세화되지 않았기 때문입니다. Bottleneck이 Bonding 기술이 아닌 기판 기술에 있다는 것입니다. 앞서 언급한대로 기판의 소재를 유리로 대체하는 것이 가장 유력한 미래 기술이며, 관련해서는 다가올 섹션에서 언급하도록 하겠습니다.

반대로 Die-Die (3D stack), Die-Interposer 사이의 Bonding은 2세대 기술인 마이크로범프를 차용합니다. 마이크로범프는 구리 기둥을 세운 뒤, 그 위에 솔더 페이스트를 올려 접착제로 활용합니다. 선폭/간격을 줄이기 위해서는 결과적으로 구리 기둥의 너비가 작아져야 하는데요. 솔더 페이스트가 올라갈 수 있는 면적이 줄어들기 때문에 자연스럽게 솔더 페이스트의 양은 줄어들게 됩니다. 접착제의 양이 적으니 적합한 bonding을 형성하는 것이 쉽지 않습니다. 이러한 한계로 인해 2세대 마이크로범프 기술의 최소 선폭/간격은 10um 수준이 될 것으로 전망됩니다.

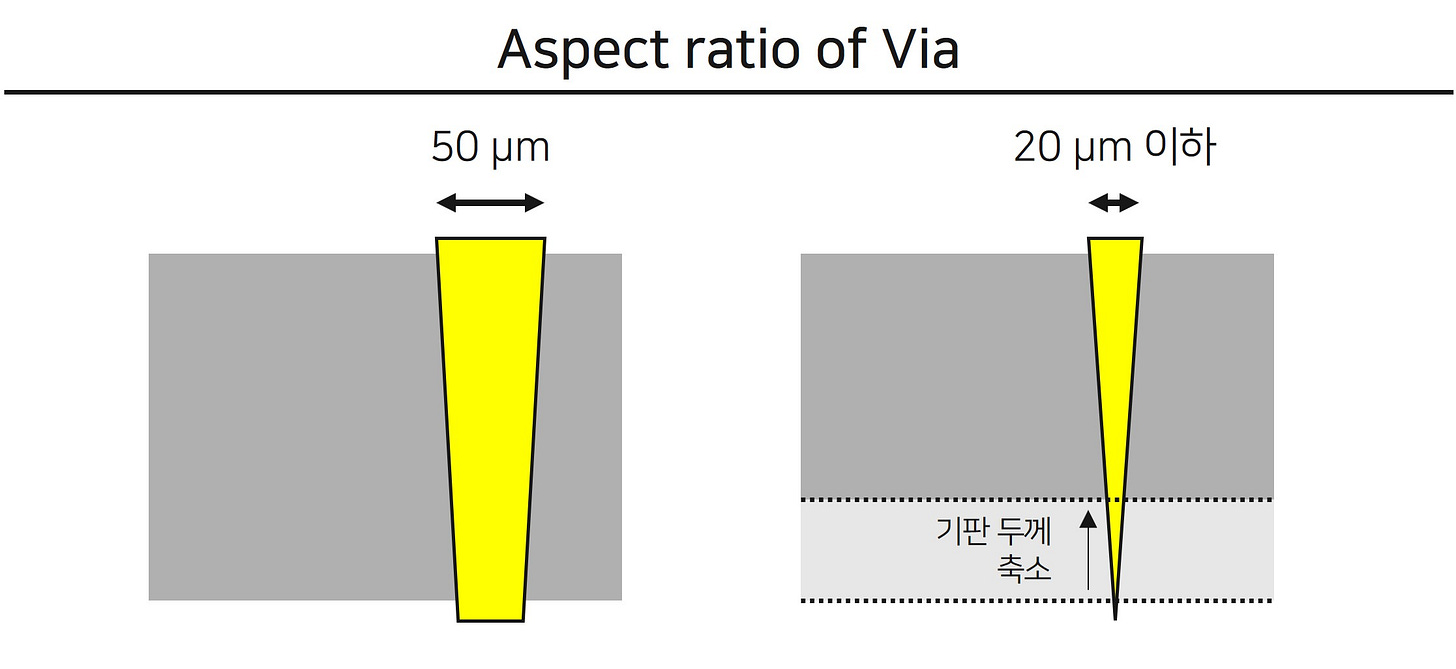

3세대 Interface Bondinig = Hybrid Bonding

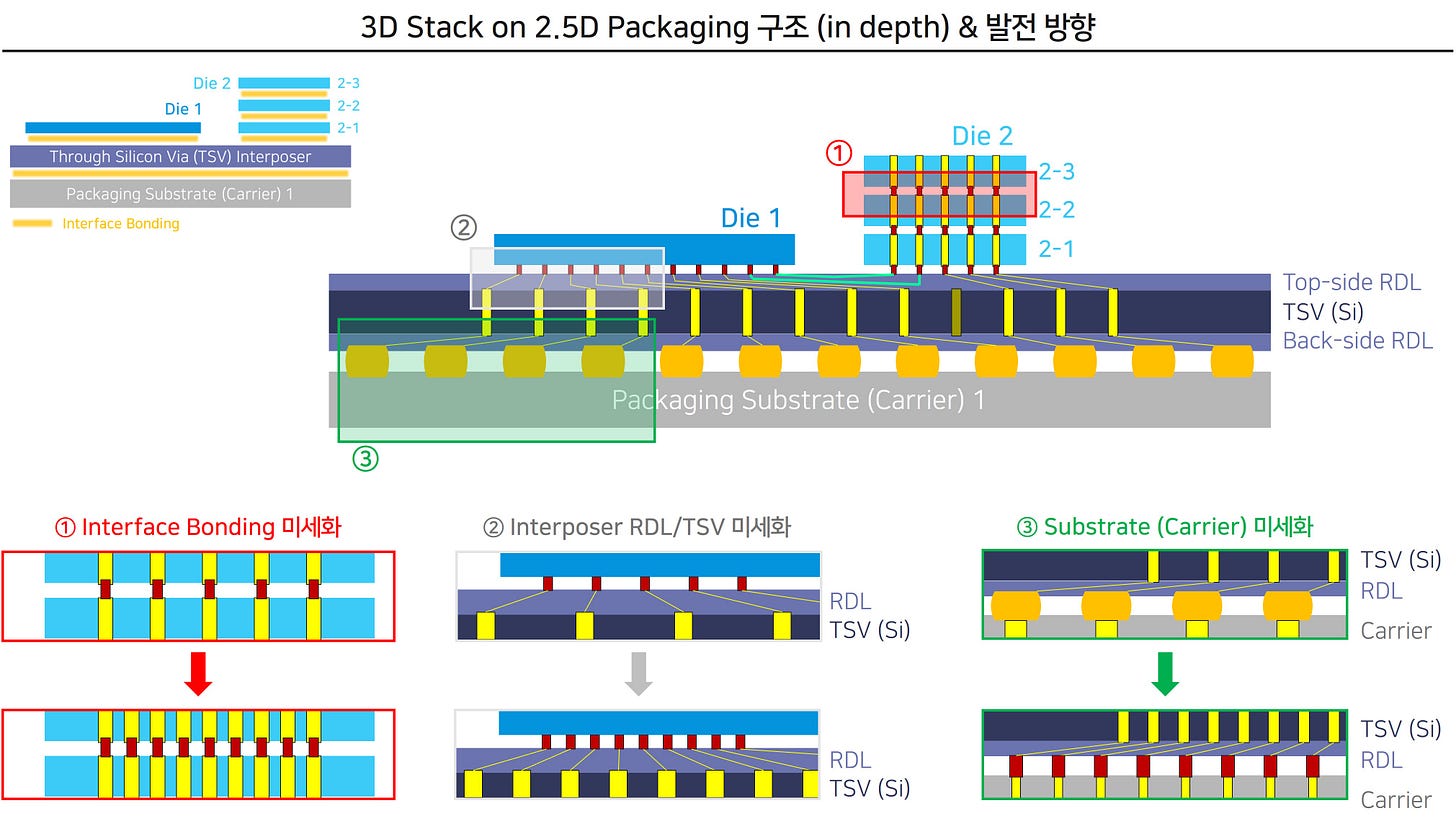

이 한계점을 넘기 위한 차세대 Bonding 기술이 바로 Cu-Cu Hybrid Bonding 기술입니다. Hybrid Bonding의 간략한 공정은 아래 그림과 같습니다:

산화물과 금속을 번갈아 증착된 구조를 만든 뒤, 산화막에 플라즈마 처리를 해 접착력을 만듭니다.

이후 상온에서 접착력이 생긴 산화막끼리 붙입니다. 낮은 온도임에도 불구하고 굉장히 강한 접착력이 발생합니다. 기계적 연결에는 성공했지만 산화막은 절연체이므로 아직 전기적 접착은 수행되지 않았습니다.

높은 온도에서 금속과 금속의 접착을 진행합니다. 금속이 산화막보다 열팽창 계수가 더 높기 때문에 가열하게 되면 산화막의 접착은 유지된 채로 금속만 팽창하여 연결되게 됩니다.

이 기술은 기존 CMOS의 Back-end of Line 공정을 접목할 수 있기 때문에 낙관적으로는 500nm 수준까지도 선폭/간격을 좁힐 것으로 전망됩니다. 이러한 낙관적인 전망을 충족하기 위해서는 크게 두 가지 선행 조건이 필요합니다.

기판이 평평해야 합니다. 선폭이 작기 때문에 기판에 약간의 roughness가 존재할 경우 금속-금속이 마주보지 않는 심각한 문제에 직면하게 됩니다.

금속과 산화물의 열팽창 특성 차이를 활용하기 때문에, 선폭이 감소함에 따라 열팽창으로 인한 뒤틀림이 발생하지 않도록 적절한 소재 조합과 온도 조건을 확보해야 합니다.

Hybrid Bonding은 이미 대규모 생산 (High Volume Manufacturing, HVM) 경험이 있는 기술입니다. 2000년 Research Triangle Institute (RTI)라는 연구소에서 Direct Bond Interconnect라는 이름으로 처음 Hybrid bonding을 제안했고, ZiBond라는 상표로 특허를 등록했습니다. 이를 Ziptronic이라는 spin-out 스타트업으로 기술이전했고, 이를 지속해서 발전시켰다고 합니다. 그리고 이 기술이 2015년 소니의 CMOS 이미지 센서를 생산하는데 활용됩니다. 현재 Ziptronic은 몇 차례의 인수 과정과 사명 변경을 거쳐 현재 Adeia라는 이름으로 영업 중에 있습니다. 하이닉스도 이 기업과 IP 라이선스를 체결하고 있고, 최근에는 Qorvo와 IP 라이선스를 체결했다고 전해집니다. 비즈니스가 쉬이 이해가지 않는 기업이지만, IP 계약의 형태나 관련 매출을 확인해보아야 할 것 같습니다. 최근에는 TSMC의 SoIC, Intel의 FOVEROS Direct 등의 기술이 가장 앞서있는 것으로 알려져 있습니다. 마찬가지로 더 상세한 내용을 다가오는 포스팅에서 다루도록 하겠습니다.

Next Generation = Interface를 없애거나 Bonding을 없애거나

Monolithic Integration = Interface를 없애는 기술

“Mono”가 숫자 ‘1’을 뜻합니다. 즉, 여러 개의 die를 다른 Lithography 공정으로 만들지 말고, 한 번의 Litho 공정으로 여러 개의 die를 쌓아 올리자는 개념입니다. 어떻게 보면 가장 이상적인 3D stack의 형태라고 할 수 있습니다. 이와 관련해서는 2015년 CEA Leti라는 프랑스의 유명한 연구소에서 진행한 “CoolCube”라는 연구가 가장 선두에 있습니다. 이 연구에서는 **3D Monlithic integration을 위해서 가장 중요한 점은 “낮은 온도에서 트랜지스터를 만드는 것”**이라고 설명합니다. 그 이유와 이를 해결하기 위한 방법까지 논문에서 다루고 있습니다만, 아직까지는 lab-scale에서만 구현된 것으로 확인됩니다. 다만 이 내용은 사실상 Packaging이 아닌 Foundry 공정 기술이기 때문에 이번 포스팅 시리즈에서는 자세히 다루지 않겠습니다.

Wireless Connection = Bonding을 없애는 기술

1,2,3 세대 기술은 모두 구리 등의 금속 선으로 연결하는 방식이었습니다. 다음 세대에는 굳이 Bonding을 하지 않아도 무선으로 연결되는 기술이 활용될 가능성이 높습니다. 이 방식이 가지는 장점은 다음과 같습니다:

Bonding 과정이 사라지며 공정 비용 감소합니다.

구리 선이 가지고 있는 전기 저항, 구리 선과 Die의 계면에서 발생하는 저항이 신호 전달의 속도를 늦추는 동시에 엄청난 열을 발생시킵니다. 이에 따라 열 관리 솔루션이 굉장히 중요하게 언급되고 있는 상황인데요. 무선으로 연결하게 되면 이러한 열 발생 지점이 상대적으로 줄어들게 됩니다.

아직까지는 패키지에서 다른 패키지로 데이터를 전송하는 IP가 주로 개발되고 있는 것으로 보입니다. 패키지-패키지 수준에서 경험을 쌓고, 향후 Die-Die에도 유사 기술을 활용할 가능성을 가늠해보아야 하겠습니다. 관련한 회로 IP 설계 기업에게 유의한 투자 기회가 있을 것으로 보이며, 국내에서는 유니컨이라는 스타트업이 눈에 띕니다.

Interface bonding의 내용을 다시 정리하면 내용은 다음과 같습니다.

1세대 솔더 볼에 머무르고 있는 Interposer-Substrate Bonding을 다음 세대로 미세화하기 위해서는 Substrate의 선폭/간격을 줄여야 합니다. 이를 해결하기 위한 방법으로 유리 기판을 활용하는 방법이 유력합니다.

2세대 마이크로범프 기술의 최소 선폭은 10um 수준일 것으로 예상됩니다. 이를 뛰어넘기 위해서는 3세대 Hybrid Bonding 기술이 활용되어야 합니다. 이 기술은 Sony의 이미지 센서 대규모 생산에 활용된 바 있고, 기술의 특허를 Adeia라는 기업이 보유하고 있습니다. TSMC는 SoIC, Intel은 FOVEROS Direct라는 이름으로 동일한 기술을 개발하고 있습니다. 관련해서 특허 Landscape을 살펴보고, 주요 기업들의 동향을 분석하면 유의한 투자 포인트가 도출될 것으로 생각됩니다.

Hybrid Bonding 이후의 기술은 Interface가 없는 monolithic integration, Bonding이 없는 무선 연결 기술이 언급되고 있습니다. Monolithic Integration에 관한 연구는 활발하게 진행되고 있으나, 이는 Packaging 기술이 아니라 Foundry 기술이라고 보아야 하기 때문에 이번 포스팅 시리즈에서는 다루지 않습니다. 무선 연결 기술 역시 무선 통신을 위한 IP를 개발하는 것이 핵심이므로 Fabless 기술이라고 생각할 수 있겠습니다. 상세히 다루지는 않습니다만, 국내 스타트업 유니컨이 향후 highlight 받을 수 있는 지점이라고 생각됩니다.

2. Interposer RDL/TSV 미세화

위 로드맵은 미국의 Semiconductor Research Corporation에서 발행한 Microelectronics and Advanced Packaging Technologies Roadmap에서 제안하는 Interposer 미세화 로드맵입니다.

사실상 Interposer 기술은 기존 CMOS Back-end of Line (BEOL) 기술과 그 궤를 같이 하기 때문에 개인적으로는 어렵지 않게 로드맵 구현에 성공할 것으로 보입니다.

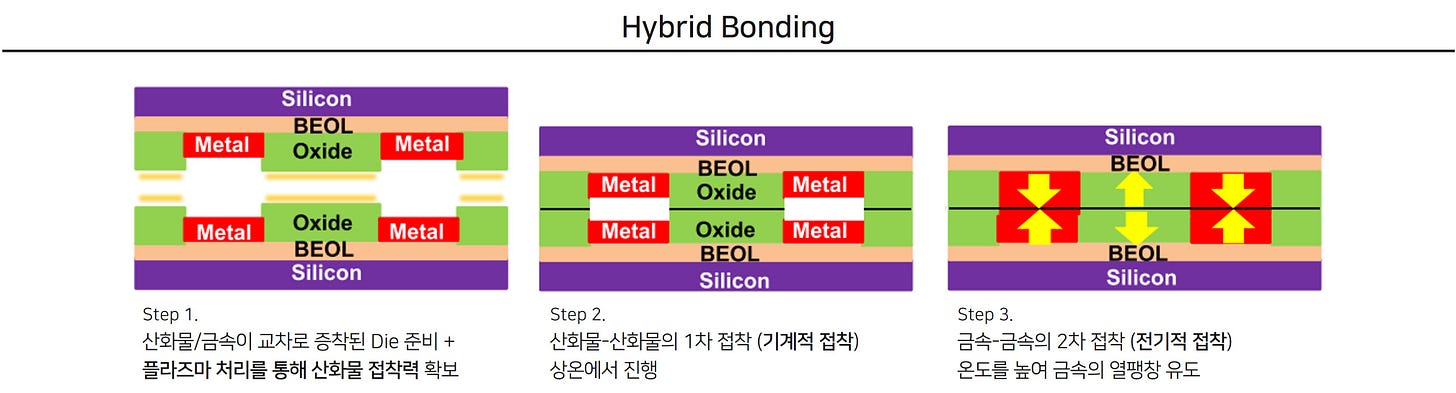

오히려 Interposer의 경우 미세한 공정을 확보하는 것보다 면적을 넓히는 것이 어려운 상황입니다. ‘25년 로드맵에 따라 50μm의 깊이를 가진 TSV를 구현하려면 실리콘 기판의 두께도 50μm로 설정됩니다. 우선, 이 정도의 미세화는 어렵지 않습니다. 참고로 HBM에서 활용하고 있는 TSV의 두께가 50μm 수준입니다. 문제는 HBM은 작은 면적의 Die 위에서 구현하지만, Interposer는 Die보다 적어도 10배는 넓은 면적으로 생산해야 한다는 점입니다. 면적이 넓어지면 기판이 휘는 문제, 기판이 깨지는 문제에 당면하게 됩니다. 더하여 Top-side RDL과 Bottom-side RDL의 두께가 다르기 때문에 온도가 높아지면 더 큰 기계적 Stress에 노출되게 됩니다.

이러한 문제를 해결하는 것은 어떤 다른 방법보다도 ‘공정 최적화’에 있습니다. 엔지니어들이 인고의 시간을

(뺑뺑이)지나겠죠..

이러한 이유로, 개인적으로는 Interposer의 미세화 과정에서 독특한 새로운 기회가 생길 것이라고 느껴지지 않습니다. 관련해서는 조금씩 자료를 수집해보고 있으며, 새로운 아이디어를 찾게 되면 빠르게 업데이트 해두도록 하겠습니다. 제가 알지 못하는 내용을 알고 계신 분께서는 언제든 댓글이나 이메일로 연락을 부탁 드립니다.

3. Substrate 미세화 → Si Photonic Integration

기존 소재의 문제점

지금까지 우리가 살펴본 모든 내용들은 “패키지 안의 Die-Die Interconnect를 늘리는 방법”에 관한 내용입니다. 하지만 우리가 모든 데이터를 하나의 패키지 안에서 생성하는 것은 아닙니다. 예를 들어, 우리가 휴대폰으로 사진을 촬영한 뒤 클라우드에 백업할 때에는 수십km 떨어진 곳에서 데이터를 주고받기도 합니다. 카메라, 텍스트, 웹 로그 등 전반적인 데이터의 양이 많아지고 있고, 데이터 센터 안에서도 엄청난 양의 데이터가 패키지 사이에서 이동합니다. 따라서 패키지-패키지 Interconnect를 늘리는 것 역시 굉장히 중요한 과제가 됩니다.

다만 지금 활용중인 BT-resin + 구리 Lamination 기술은 한계가 명확합니다. 기판은 위-아래 방향으로 데이터를 전송하는 역할을 합니다. 따라서 Interposer의 Through Silicon Via (TSV)처럼 기판에도 수직 방향으로 형성된 구멍인 via을 뚫어야 하는데요. via는 위아래로 무한정 길어질 수가 없습니다. 아래 그림처럼 구멍의 크기가 작아지면 기판의 두께도 얇아져야 합니다.

따라서 선폭/간격을 줄이려면 소재를 얇게 만들어서 가공해야 하는데, 현재의 BT-resin core는 기계적 강도가 약해 얇아지면 스르륵 혼자 구부러집니다. 또, 앞서 Hybrid bonding에서 언급한대로 선폭이 작아질수록 표면이 매끄러워야 하는데, 지금의 BT-resin core 소재는 굉장히 거친 표면을 가지고 있습니다. 따라서 소재의 변화가 필요합니다.

유리 기판의 부상

가장 쉽게 접근할 수 있는 후보가 바로 실리콘 기판입니다. 하지만 실리콘 기판은 상상 이상으로 쉽게 부러지고 깨지기 때문에 패키지 크기를 늘리기 어렵습니다. (Interposer와 같은 흐름입니다.)

그렇게 돌아 돌아 가장 유의한 후보군으로 남은 것이 유리입니다. 얇게 저며도 쉽게 구부러지지 않는 강인한 기계적 특성, 아주 매끈한 표면 등 드러나는 특성에서도 유리합니다. 덤으로, 절연 특성이 굉장히 좋아서 미세화 이후 발생할 수 있는 신호 손실이나 cross-talk의 문제에서도 자유롭습니다.

이런 이유로 23년 9월 인텔이 자신있게 유리 기판 공정을 공개했고, SKC는 미국 조지아에 큰 돈을 투자해 유리 기판 공장을 설립하기 시작합니다.

유리 기판을 활용하기 어려운 이유는 잘 깨진다는 것, 금속 박막과의 접착성이 좋지 않다는 것, 유리 기판끼리의 접착이 어렵다는 것 세 가지 정도로 파악됩니다.

유리 기판은 패키징 공정에도 큰 영향을 미치며, 기판 제조 value chain이 전반적으로 전환되는 기폭제가 되므로 중요한 투자 지점이 될 것으로 기대됩니다. 관련해서는 별도의 포스팅으로 다루겠습니다.

차세대 패키지-패키지 Interconnection = 광통신 (Silicon Photonics)

유리 기판 이후의 Package-Package Interconnection은 실리콘 기반의 광통신이(Photonics) 될 가능성이 높습니다. 구리 전선은 불가피한 저항이 존재하기 때문에 데이터 전송이 많을 경우 많은 열과 신호 손실이 발생합니다. 반대로 광통신은 저항이 존재하지 않기 때문에 열 발생과 신호 손실을 방어할 수 있습니다.

광통신 기반의 패키지-패키지 Interconnection이 가능해지기 위해서는 Laser, Waveguide(광섬유), 렌즈 등 기존과는 다른 Die의 패키지 integration 기술이 필요해집니다. Electronic IC(EIC)와 Photonic IC(PIC)를 하나의 패키지 안에 integration해야 하는데요. 관련해서 제가 접한 기술은 인텔의 Silicon Photonics Connect 기술입니다. 아직은 R&D 단계에 있는 것으로 확인되며, 연구 동향에 대한 리뷰 논문을 첨부합니다. 마찬가지로 이 기술이 구현될 경우 데이터 센터의 퍼포먼스 증가와 함께 운영 비용(냉각)이 극적으로 낮아질 수 있기 때문에, 관련해서 별도의 포스팅으로 다루도록 하겠습니다.

결론

반도체 Packaging의 핵심 현안은 다음과 같음:

Package 하나에 더 많은 Die를 넣기 위해 기판 면적을 늘리고, 3D Stack 강화

Die들의 효과적인 Computing을 위해 Die-Die를 연결하는 Interconnect의 개수 확대 (=미세화)

이번 포스팅에서는 미세화 과정에 대해 상세히 다룸. 미세화 과정에는 다양한 기술적 변화가 필요하므로 기존에 주목받지 않던 player에게 새로운 기회가 있을 것으로 기대.

미세화 과정에서의 기술 변화 흐름은 다음 세 가지로 정리됨:

Interface Bonding 미세화: Cu-Cu Hybrid bonding의 본격화 + 특허 이슈 확인 필요

Interposer RDL/TSV 미세화: 기존 Interposer 제조 업체의 생산 능력 강화 예상

Packaging Substrate (Carrier) 미세화: Glass 기판 및 Glass 공정 유관 소재 업체에 새로운 기회가 생길 것 + 광통신 기술이 데이터 센터 운영의 패러다임을 바꿀 것

두 번째 포스팅을 지나며 패키징 산업에서 다가올 주요 기술에 대해 중요한 지점들이 하나 둘 나오기 시작했습니다. 하지만 미세화 공정이 성공적으로 수행될 수 있다고 해도 다가오는 문제들이 이만저만이 아닙니다. 대표적인 문제가 과도한 열 발생입니다. 데이터 이동이 많아지며 엄청난 양의 열이 발생하고, 3D Stack으로 켜켜이 쌓인 다른 칩들 때문에 열이 쉬이 빠져나가지 못하면서 패키지 전체가 제대로 작동하지 못할 수 있습니다. 다음 포스팅에서는 이렇게 미세화 공정이 고도화되며 파생되는 다른 문제점들을 살펴보고, 이를 해결하기 위한 기술의 꼭지를 찾아봅니다. 오늘도 긴 글 읽어주셔서 감사합니다. 다음 포스팅에도 많은 관심 부탁 드립니다!