Semiconductor Packaging 분석 시리즈

Highlights

반도체 Packaging 구조가 왜, 그리고 어떻게 변화했는지 전반적인 내용 정리

Mainstream 기술은 3D Stack on 2.5D Packaging 기술이며, 향후 발전 방향은 다음과 같음:

(More Dies on Package) 3D Stack 고도화, 대면적 interposer

(Low Cost Application) 2.3D & 2.1D 구조 수율 확보

(Higher Interconnect Density) Bonding pitch 최소화 for die-to-die, Glass substrate for package-to-package

안녕하세요, 구독자 여러분. WAGU입니다. 이번 시리즈에서는 반도체 Packaging 산업을 살펴봅니다. 난이도가 낮지 않은 기술 산업이기에 이번 주에 연재 될 3개의 포스팅에서는 전반적인 기술을 소개하고, 뛰어넘어야 할 기술적 허들을 가늠합니다. 이후 기획 중인 포스팅에서는 각각의 기술적 허들을 해결해가는 기업들을 살펴보며, 투자 포인트를 도출하고자 합니다. 긴 시리즈가 될 것 같습니다. 끝까지 호흡을 함께해주시면 감사하겠습니다.

CMOS 공정이 한계에 다다르고 있습니다. 반도체 성능을 극대화하기 위해 기업들은 선폭을 줄이는 것이 아닌, 회로 설계를 수정하고 공정을 최적화하는 방법을 선택하였는데요. 최근에는 이 방법까지 한계에 다다르며 상대적으로 관심 밖에 있던 Packaging이 중요 화두로 떠오르기 시작했습니다. 이러한 시장 환경은 이미 Packaging 산업을 매력 있게 조명합니다. 개인적으로 Packaging 산업에 주목했던 또 다른 이유는 (1) 생각보다 발전의 여지가 많이 남아있고, (2) 새로운 value chain이 조명받을 수 있는 넓은 산업 landscape를 가지고 있기 때문입니다.

대부분의 자료가 선폭 미세화 자체에 대해 다루고 있는데요. 이번 포스팅 시리즈에서는 미세화되는 과정에서 파생되는 새로운 문제를 해결하기 위한 전력 반도체 소재와 집적화 기술, Signal Processing IP에서 새로운 투자 기회가 있을 것이라는 결론을 도출합니다. 더해서 다음 세대의 기술로 Die-to-Die Wireless 연결 기술 (우리나라 스타트업 유니컨이 떠오릅니다!), Photonics 기반 연결 기술도 중요 투자 지점으로 다룹니다.

이 결론에 도달하기 위해 이번 포스팅에서는 Packaging 구성 요소들이 배치되는 구조를 아주 간단하게 살펴봅니다. (이를 만들기 위한 공정이나 세부적인 내용은 다루지 않습니다.) 또한 구조 변화에 대한 논리적인 이해를 위해 몇몇 설명은 순서나 논리의 전개가 온전한 실제와 다를 수 있습니다. 관련해서 더 상세한 기술적인 내용이 궁금한 분들께서는 Unimicron CTO인 John Lau가 저술한 책 혹은 review 논문을 참조하는 것을 추천합니다.

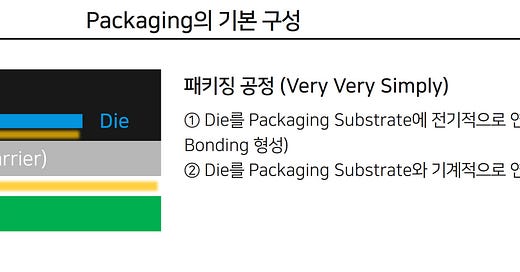

Packaging의 기본 구성

반도체 Packaging은 기능을 가진 Die를 기계적, 전기적으로 외부와 연결하는 과정을 의미합니다. 풀어 설명하자면 (기계적) 딱딱하고 잘 부러지지 않는 구조물과 접착하는 한편, (전기적) 이 구조물에 안착된 전선과 연결하는 과정입니다.

Packaging의 기본 구성도 이 정의에 기반해 정리할 수 있습니다.

딱딱하고 잘 부러지지 않는 구조물 = 회색 Packaging Substrate (or Carrier)

기계적인 접착 = 검정색 Molding

전선의 연결 = 노란색 Interface Bonding

초록색으로 표시된 Motherboard (PCB) 역시 큰 의미에서 부러지지 않는 다른 구조물이 됩니다. 이번 포스팅에서는 Motherboard는 Packaging의 일부로 고려하지 않겠습니다.

이러한 간단한 구성 하에, Packaging은 다음과 같은 아주 간단한 프로세스로 진행됩니다.

Die를 Packaging Substrate에 전기적으로 연결해 노란색 Interface Bonding을 형성하는 과정

Die를 Packaging Substrate와 기계적으로 연결해 검정색 Molding을 형성하는 과정

Interface Bonding과 Molding을 형성하는 과정도 세세히 살펴보면 많은 공정/소재 기술이 필요하지만, 이번 포스팅에서는 다루지 않겠습니다.

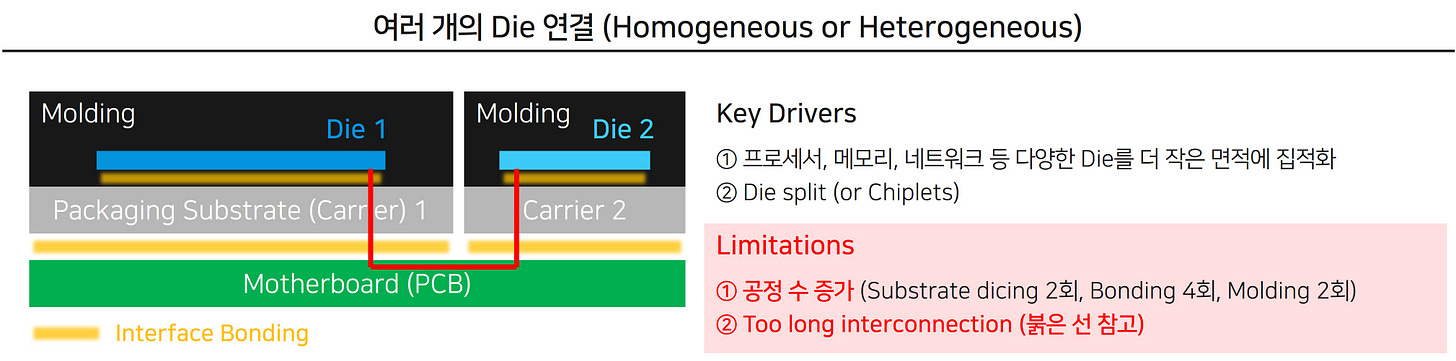

Die Integration에 대한 Needs와 기존 방식의 한계점

Needs (or Key Drivers)

현재 컴퓨팅 방식인 폰 노이만 구조에서는 프로세서 - 메모리, 최소 두 개 이상의 Die가 필요합니다. 스마트폰의 경우, 여기에 무선 네트워크용 Die도 필요합니다. 여러 개의 Die를 하나의 System에 통합하고자 하며, 더 작은 면적에 집적하려고 합니다.

Die 하나의 크기가 증가할수록 CMOS 공정의 수율은 감소하고, 버려지는 Wafer의 양은 많아집니다. 최근에는 Multi-core CPU를 여러 개의 Single-core CPU unit으로 나누어 생산한 뒤, 이를 Packaging 과정에서 붙이는 chiplet design이 중요하게 다루어집니다.

Limitations

하지만 이렇게 여러 개의 die를 각각 Packaging한 뒤, 다시 Motherboard에 실장하는 과정을 거치면 공정의 수가 증가하게 됩니다. Die 2개를 붙이는 데에는 Carrier를 적합한 크기로 자르는 dicing 과정 2회, Bonding 과정 4회, Molding 과정 2회가 필요합니다.

Die 사이의 간격이 너무 길어집니다. 위 그림의 붉은 선과 같이, Die 1에서 출발한 신호는 첫 번째 Carrier를 지나 Motherboard를 거쳐, 두 번째 Carrier를 통과한 뒤에야 Die 2에 도달하게 됩니다. 간격이 길어지면 신호 전달 속도가 느려진다는 문제가 생깁니다.

2D Packaging의 등장

Improvement = 하나의 Carrier에 여러 개의 Die를 붙이는 기술 = System in Package (SiP)

단순히 하나의 Carrier에 두 개의 Die를 올리는 구조의 변화로, 공정은 3단계나 감소하게 됩니다. (기존 Dicing 2회 + Bonding 4회 + Molding 2회 → SiP Dicing 1회 + Bonding 3회 + Molding 1회)

위 그림의 붉은 선과 같이, Die 1에서 출발한 신호는 더 이상 Motherboard까지 가지 않고도 Die 2에 도달할 수 있게 되면서 신호 전달 거리가 감소합니다. 신호 전달 거리가 감소하며 전달 속도 증가, 신호 손실 최소화, 열 발생 최소화 세 마리 토끼를 잡을 수 있게 됩니다.

Limitation

Interconnect 거리는 짧아졌지만, 이제는 Interconnect의 숫자를 늘리고 싶습니다. 전선을 더 촘촘히 배치해야 한다는 의미입니다. 하지만 활용 중인 BT resin + Copper lamination 기반의 현재 Carrier는 전선을 촘촘히 배치하기 어려운 소재입니다.

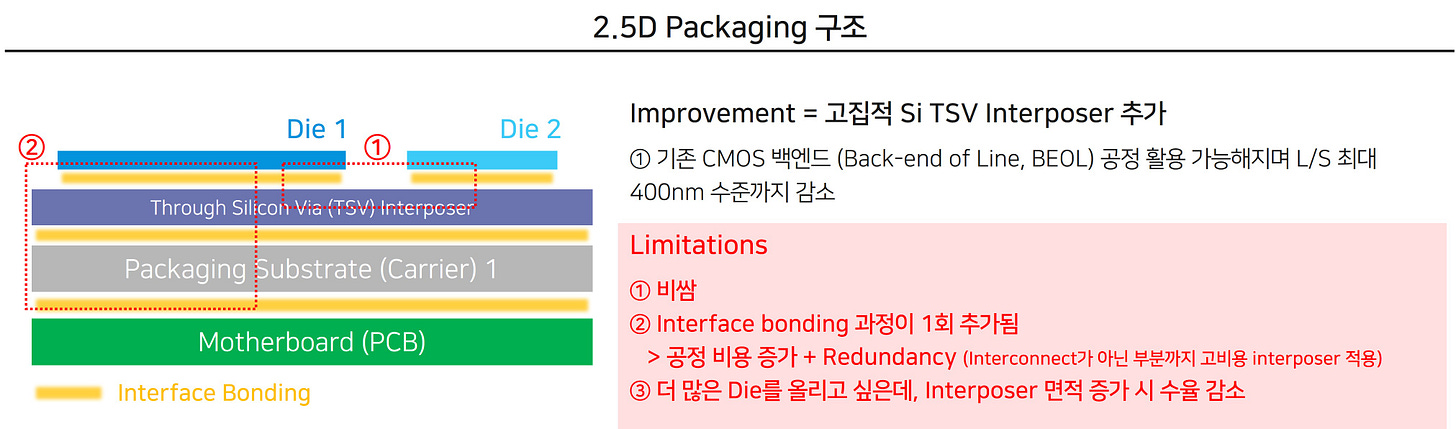

2.5D Packaging = Si(실리콘) Through Silicon Via(TSV) interposer

Improvement = 고집적 Si TSV Interposer 추가

실리콘 기판을 활용합니다. 실리콘 기판에서는 기존 반도체 공정을 활용할 수 있어 굉장히 촘촘한 배선을 구현해낼 수 있습니다. Carrier 대비 최대 100배 촘촘한 배선이 가능해집니다. (배선 간격 - 기존 Carrier 50 μm → Si Interposer ~400nm)

Limitation

비쌉니다. 특히 위-아래를 연결하기 위해 Through Silicon Via (TSV) 라는 기다란 구멍을 뚫고 그 구멍에 금속을 넣어야 하는데요. 이 과정이 생각보다 수율이 낮고 공정 비용도 큽니다.

Interposer와 Carrier 사이에 노란색 Interface Bonding 공정이 1차례 추가됩니다.

당연히 공정 비용이 증가합니다.

(붉은 상자 ①) Interposer는 Die 1과 Die 2의 연결을 촘촘하게 만들기 위해 필요합니다. 하지만 (붉은 상자 ②) Die와 Carrier 사이의 연결에는 고성능 Interposer가 필요하지 않습니다. 어차피 Carrier의 배선 간격에 의해 성능이 좌우되기 때문입니다. 붉은 상자 ② 부분은 굳이 고성능 Interposer를 활용할 필요가 없으므로, 일종의 낭비입니다. 조금 더 멋들어진 용어로는 Redundant 하다고 이야기합니다.

지금 이 그림에서는 Die 2개를 Packaging하는 과정에 대해서만 언급하고 있습니다. 하지만 인간의 욕심은 끝이 없고, 더 많은 Die를 올리고자 합니다. Si interposer를 더 넓게 만들어 Die 개수를 늘리고자 하지만, 면적이 넓어질수록 수율이 낮아지며 가격은 더 비싸집니다.

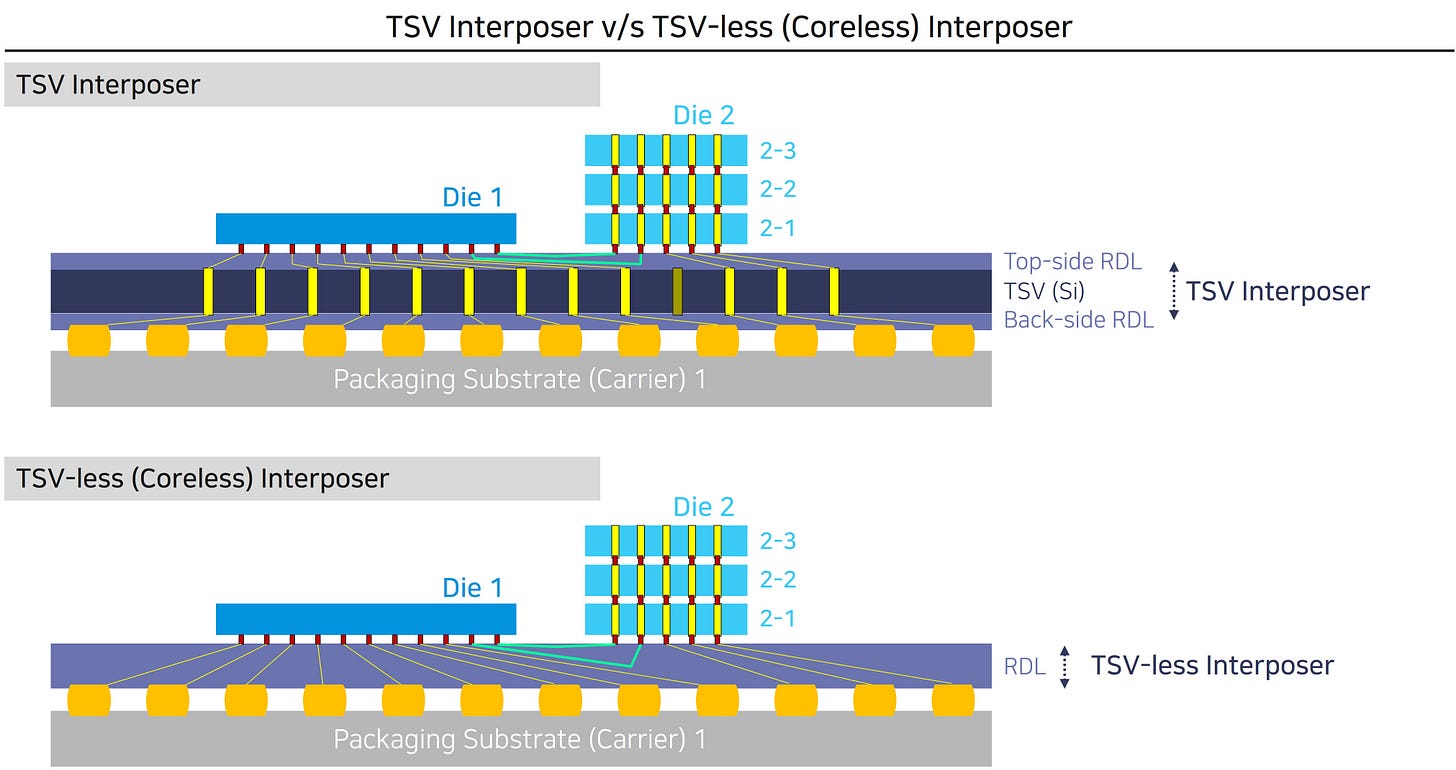

2.3D Packaging = TSV-less Interposer 활용

Improvement = 비용이 적은 Redistribution Layer (RDL) Interposer 적용 (or TSV-less)

TSV 형성 난이도와 비용이 높으므로, 이를 제외하고 RDL만을 활용해 만든 Interposer를 활용합니다. RDL은 아래 그림과 같이 공간적으로 배선을 옮기는 촘촘한 전선 층을 의미합니다. 사실상 TSV Interposer와 TSV-less Interposer의 기능은 동일합니다. 차이점은 TSV Interposer는 실리콘 기판 양쪽에 RDL이 붙어있고, TSV-less Interposer의 경우는 가운데 실리콘 기판 없이 RDL만 형성한다는 것입니다. 이런 이유로 TSV-less Interposer를 Coreless Interposer라고 부르기도 합니다.

강조하자면 TSV-less Interposer는 기능 고도화보다 비용 절감에 초점이 맞추어진 기술입니다. 실제로 TSV-less Interposer는 TSV Interposer보다 배선 간격이 더 넓고, 표면의 굴곡이 더 심하기 때문에 미세 공정을 수행하기에 적합하지 않습니다. 하지만 특정 Die-Die 연결에는 굳이 TSV Interposer 수준의 고밀도 연결이 필요하지 않을 수 있습니다. 이런 경우 TSV-less Interposer를 활용하는 것이 훌륭한 가성비 옵션이 될 수 있는 것이죠.

맛보기로만 언급하자면, TSV-less Interposer를 만들기 위해서는 Ajinomoto Build-up Film (ABF)라는 소재가 필요합니다. 분명 유의한 투자 지점이 있을 것이라고 생각합니다. 아직 저는 탐색 단계에 있습니다. 포스팅 업데이트 이전에 공부하고 싶은 분들을 위해 논문을 첨부합니다. (논문 1, 논문 2, 논문 3, 논문 4)

Limitation

이론상 저렴하지만, 아직까지 개발된 공정으로는 TSV-less interposer가 더 비쌉니다(ㅠㅠ). TSV-less Interposer 자체를 제조하는 데 필요한 비용도 아직은 높은 편이고, Interposer와 Die를 연결하는 Interface Bonding에서도 수율 loss가 높은 것으로 확인됩니다.

구조가 2.5D와 동일하기 때문에 다른 한계점들을 공유합니다.

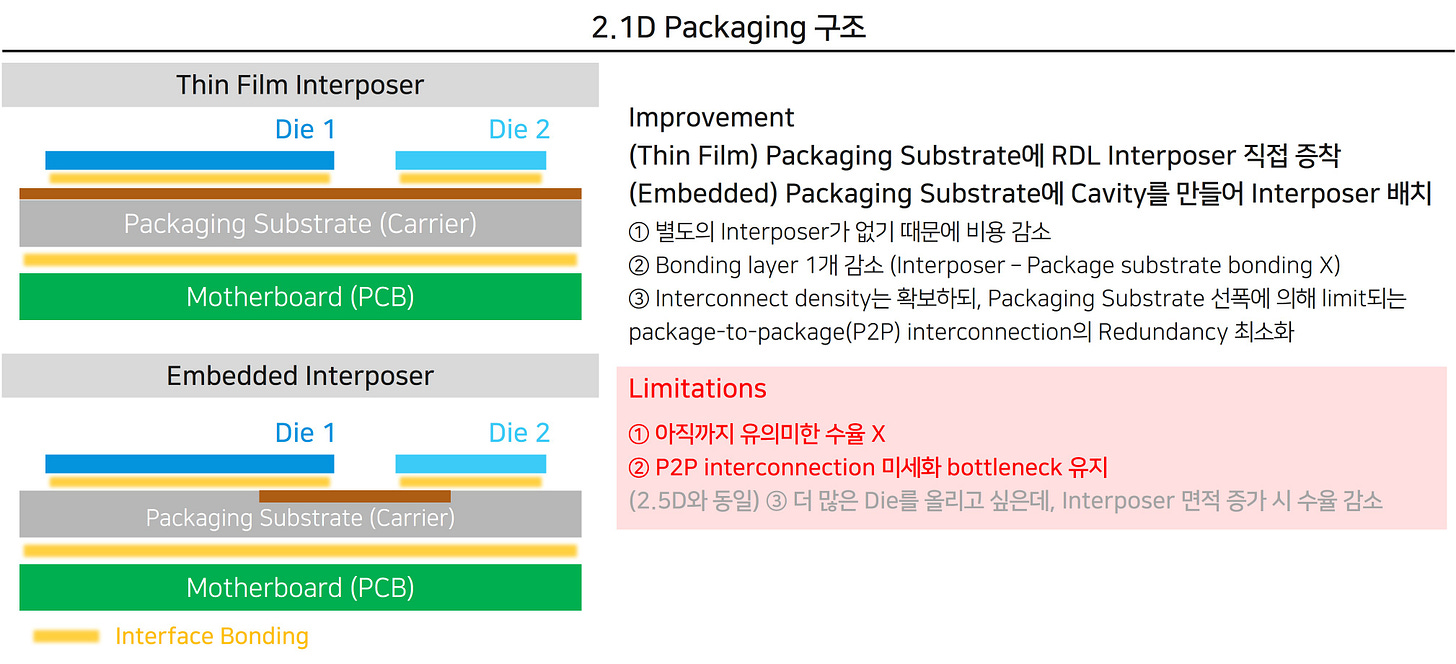

2.1D Packaging = 박막 혹은 Embeded Interposer

Improvement = Carrier에 직접 Interposer 배치

2.1D 구조에서는 (Thin film) Carrier에 RDL Interposer를 직접 증착하거나, (Embedding) Carrier에 작은 Cavity를 만들어 그 안에 Interposer를 배치하는 방법을 차용합니다.

(박막 증착) 별도 Interposer 제조 공정이 없어지거나, (Embed) 작은 Interposer를 제조하게 되어 비용이 감소합니다.

Interposer - Carrier의 Interface Bonding이 사라집니다. Bonding 공정이 하나 사라지므로 비용이 감소합니다.

2.5D에서 강조했던 redundancy 문제에서 자유롭습니다. Interconnection 이외 지역에서 불필요한 RDL이 사라지며 신호 전달 경로가 짧아지고 비용도 감소합니다.

참고로, Intel은 2014년부터 2.1D 구조인 Embedded Multi-Die Interconnect Bridge (EMIB) 관련 특허를 등록하고 있습니다. 2017년 KabyLake 프로세서에서 EMIB를 활용했으나, 이후 세대에서는 활용되지 않는 것으로 확인됩니다. 상용화 역사가 있는 만큼 멀지 않은 미래에 다시 조명될 것으로 기대합니다.

관련해 참고하실 수 있는 논문을 첨부합니다. (논문 1)

Limitation

수율이 낮습니다.

Package 바깥으로 빠지는 정보의 양은 여전히 Carrier의 배선 간격에 의해 좌우됩니다. 이제는 Package 안에서 Die-to-Die Interconnection을 극대화했으니, Package 밖에서 이루어지는 Package-to-Package Interconnection을 극대화해야 하는 시점입니다.

2.1D 역시 Interposer를 활용한다는 측면에서 2.5D와 동일하기 때문에 더 많은 Die를 올리기 위해서는 기판 면적을 늘려야 한다는 문제에 봉착합니다.

2.1D Packaging on Glass Substrate

Improvement = Carrier 재료 교체

2.1D와 동일한 구조이지만, Carrier의 재료가 바뀝니다. 기존의 BT resin + Copper Lamination 소재는 좋아봐야 50 μm 수준의 배선 간격을 가지지만, Glass는 수 μm 수준까지 간격을 좁힐 수 있습니다. Wow! (적어두고 보니 좀 너드같네요.)

다시 강조하자면 지금까지는 Package 안에서 Die-to-Die Interconnection에 집중해왔습니다. Package-to-Package Interconnect는 기존의 Conventional Packaging 수준에 머무르고 있습니다. Data Center 내의 모든 Die를 하나의 패키지로 만들지 않는 한, Package-to-Package (P2P) 사이의 데이터 교환 역시 중요하게 다루어져야 합니다. 이에 따라 Glass Substrate의 중요성은 점점 더 강조될 것이며, 관련해서는 별도의 포스팅에서 자세히 다루도록 하겠습니다.

Limitation

매우 잘 깨집니다. Chip/Die Packaging 이후 이를 운송/판매하고, 구매한 기업이 System packaging을 진행하는 것이 현재의 비즈니스 구조인데요. Chip/Die packaging이 잘 깨지는 상황이므로 아예 한 공정 라인에서 System Packaging하는 방식으로 문제를 어느 정도 완화할 수 있겠습니다. 다만, 이런 경우 공정 병렬화가 어려워 고객을 한 곳만 받을 수 있는 문제가 생길 수도 있습니다. 관련한 현황을 3월 중으로 업데이트할 예정입니다.

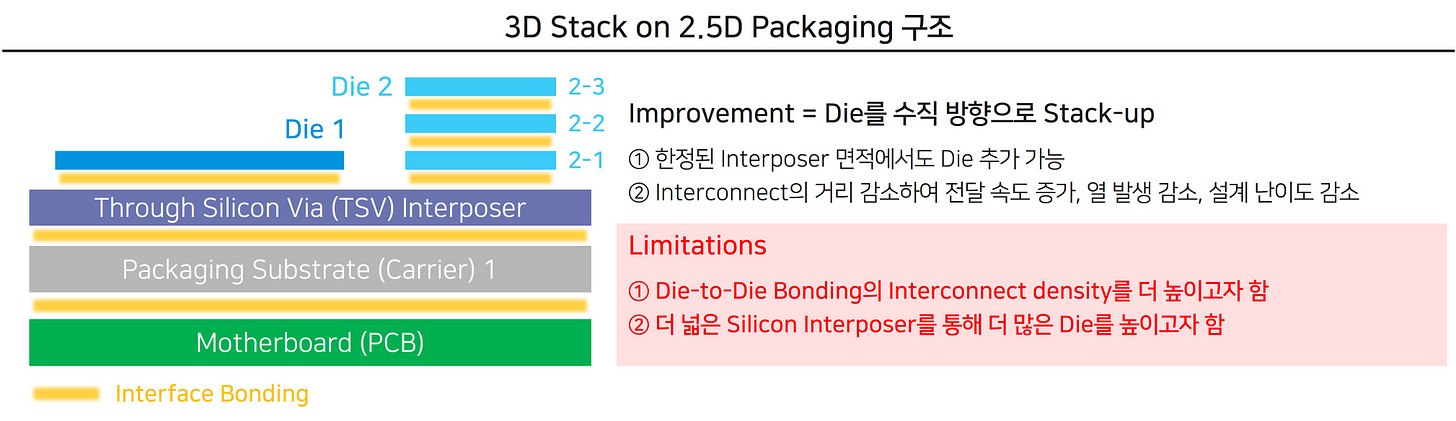

3D Stack on 2.5D Packaging = 무한히 많은 Die를 올려보자.

Improvement = Die를 수직 방향으로 Stack-up

한정된 Interposer 면적 안에서도 Die를 추가할 수 있습니다.

수평으로 Die를 연결하는 것보다 수직으로 연결할 때 Interconnect의 거리가 감소합니다. 처음 2D Packaging 구조를 설명했을 때와 같이, Interconnect 거리 감소는 전달 속도 증가, 신호 loss 및 열 발생 감소의 장점을 가집니다. 더하여, 복잡한 RDL 설계가 사라지며 설계 난이도도 감소하게 됩니다.

위 같은 구조가 최근 가장 성능 좋은 Processor (Die 1) - HBM (Die 2) 조합에서 살펴볼 수 있는 구조입니다. State-of-the-Art (SOTA) 구조라고 할 수 있겠네요.

Limitation

우선 수율에 대한 까다로운 기준이 생기게 됩니다. 지금 위 그림에서는 Die가 총 4개 붙어있는데요. 이들 중 1개의 Die에서 문제가 발견되면 4개의 Die를 모두 버려야 합니다. 따라서 하나의 Package 위에 더 많은 Die가 붙을수록 이미 성능이 검증된 Die만을 활용해야 합니다. 이를 Known Good Die (KGD) Packaing이라고 합니다. 다르게 이야기하면.. 검증된 Die만 활용했으므로 Packaging에서 실수가 생기면 엄청난 비용이 발생하는 것입니다. 신뢰성이 중요해지므로 Captive Network가 더욱 공고해질 가능성이 높습니다. 지금 형성된 클라이언트-고객 관계를 다시 점검하는 것만으로도 유의미한 투자 지점을 찾을 수 있을 것으로 판단됩니다. (역시 다가오는 포스팅에서 다루도록 하겠습니다. 넓디 넓은 Packaging의 세계..)

(인간의 끝없는 욕심)Die-to-Die Stack 과정에서 Interface Bonding의 Interconnect density를 더 높이려고 합니다. 더 넓은 Interposer를 통해 더 많은 3D-stacked die를 붙이려고 합니다. 신뢰성 있는 Stack 공정을 통해 10층, 20층 더 높은 3D-stack을 만드려고 합니다.

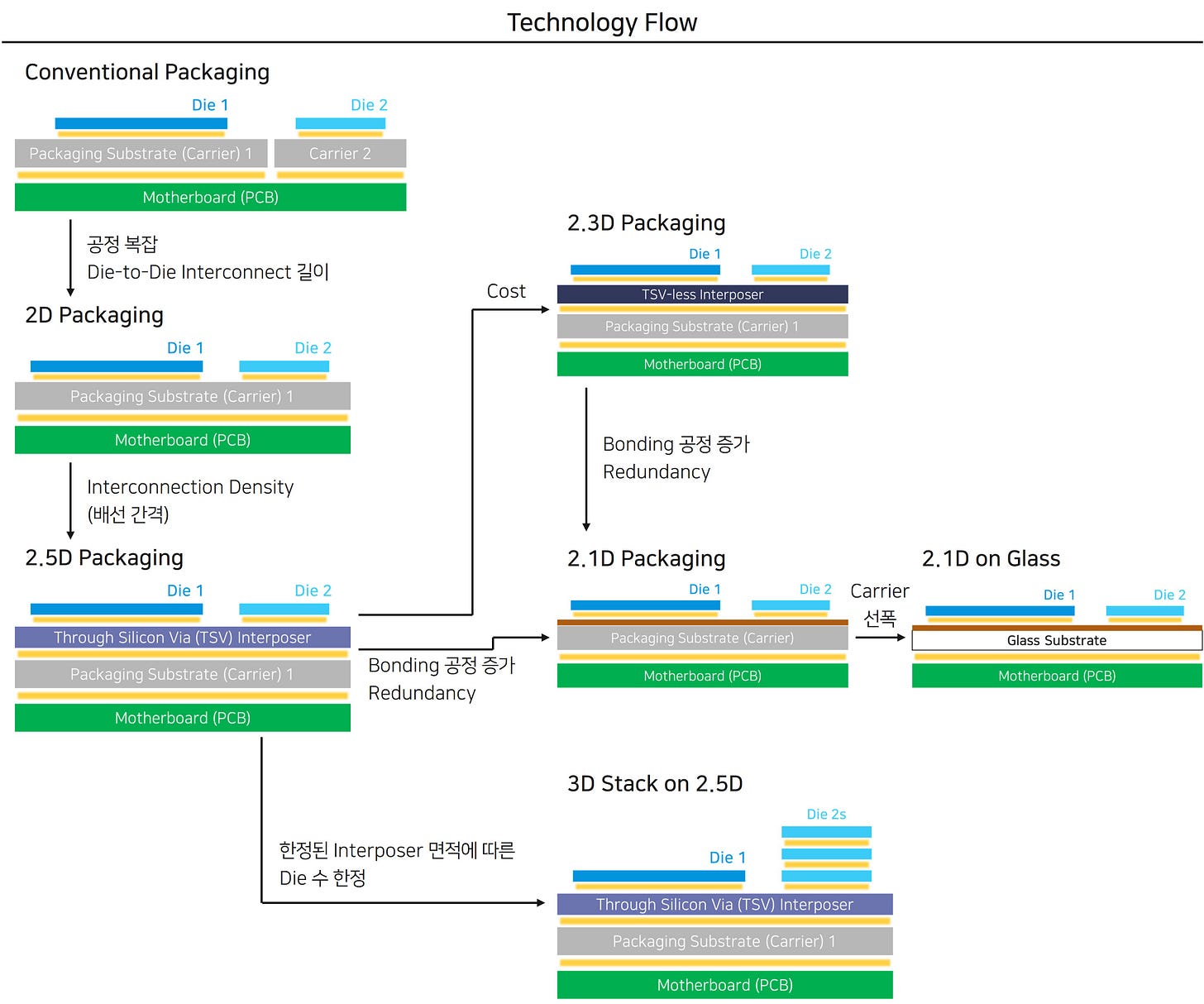

정리 및 결론

이번 포스팅의 내용을 하나의 그림으로 정리하자면 아래 그림과 같습니다:

현재의 SOTA 기술은 3D Stack on 2.5D입니다.

향후 핵심 Milestone은 3D Stack on 2.1D (Glass)가 될 것으로 판단됩니다만, Glass 기판의 강력한 경쟁 상대로 Silicon Photonics Integration이 있습니다. 이에 관해서는 다가올 포스팅에서 자세히 다루겠습니다. (몇 개나 있는걸까요?)

SOTA에서 향후 발전 방향은 다음과 같습니다:

(More Dies on Package) 3D Stack 고도화, 대면적 interposer

(Low Cost Application) 2.3D & 2.1D 구조 수율 확보

(Higher Interconnect Density) Bonding pitch 최소화 for die-to-die, Glass substrate for package-to-package

모두 긴 글 읽으시고, 많은 정보를 입력하시느라 고생하셨습니다. 금일 업데이트 이후 몇 차례 수정을 진행할 예정입니다. (논문 첨부나 일부 표현에서의 아쉬움이 남아있습니다.) 상세한 공정이나 소재에 관한 내용 없이 구조에 대한 내용만을 다룸에도 상당히 많은, 유의미한 Implication이 있었다는 점이 나름의 뿌듯함입니다. 다가오는 포스팅에서는 먼저 SOTA에서 미세화를 수행하기 위한 기술에 관해 설명합니다. 위 결론에서는 Higher Interconnect Density에 해당하는 내용입니다. 3/7 이전에 업로드될 예정이니, 계속해서 많은 관심 부탁 드리겠습니다!

Great post. Thx!