Semiconductor Packaging 분석 시리즈

Industry | Semiconductor Packaging (5) Hybrid Bonding

Key Opportunities

공정 프로세스가 이전 패키징 프로세스와 완전히 달라지기 때문에 관련된 value chain 상에서 전반적인 구조적 성장이 기대됨. 그들 중 가장 매력 있는 기회라고 판단되는 것은 다음과 같음:

Hybrid bonding 시장은 현재 개화 중이며, Direct D2W Bonding 장비 개발 기업이 시장 개화를 주도하고 유의한 기술적 해자를 유지해갈 것으로 판단 = BESI, ASMPT

프로세스 중 플라즈마를 활용하는 단계 급증 (PECVD, Plasma Activation, Plasma Dicing)

세 가지 공정에서 모두 필요한 소모품에 대한 Needs 급증 = 플라즈마 Generator 시장

Plasma Dicing의 경우 기존 식각 공정 대비 더 강한 에너지의 플라즈마 활용, 소모품 교체 주기 압도적으로 빨라질 것 = 식각 장비 관련 소모품 (Etching Ring 등) 시장

W2W, Di-D2W 특허 포트폴리오 1위 TSMC, 2위 Adeia. TSMC 시스템을 활용하지 않을 경우 Adeia와 IP 라이선스 계약이 강요될 수 있음. 현재 다수 (W2W) 3D NAND, 3D DRAM / (Di-D2W) HBM 기업들이 Adeia와 라이선스 계약 체결. 계약 조건을 살펴보아야 하지만 Hybrid bonding 시장 개화에 발맞춘 실적 증가 기대.

Landscape

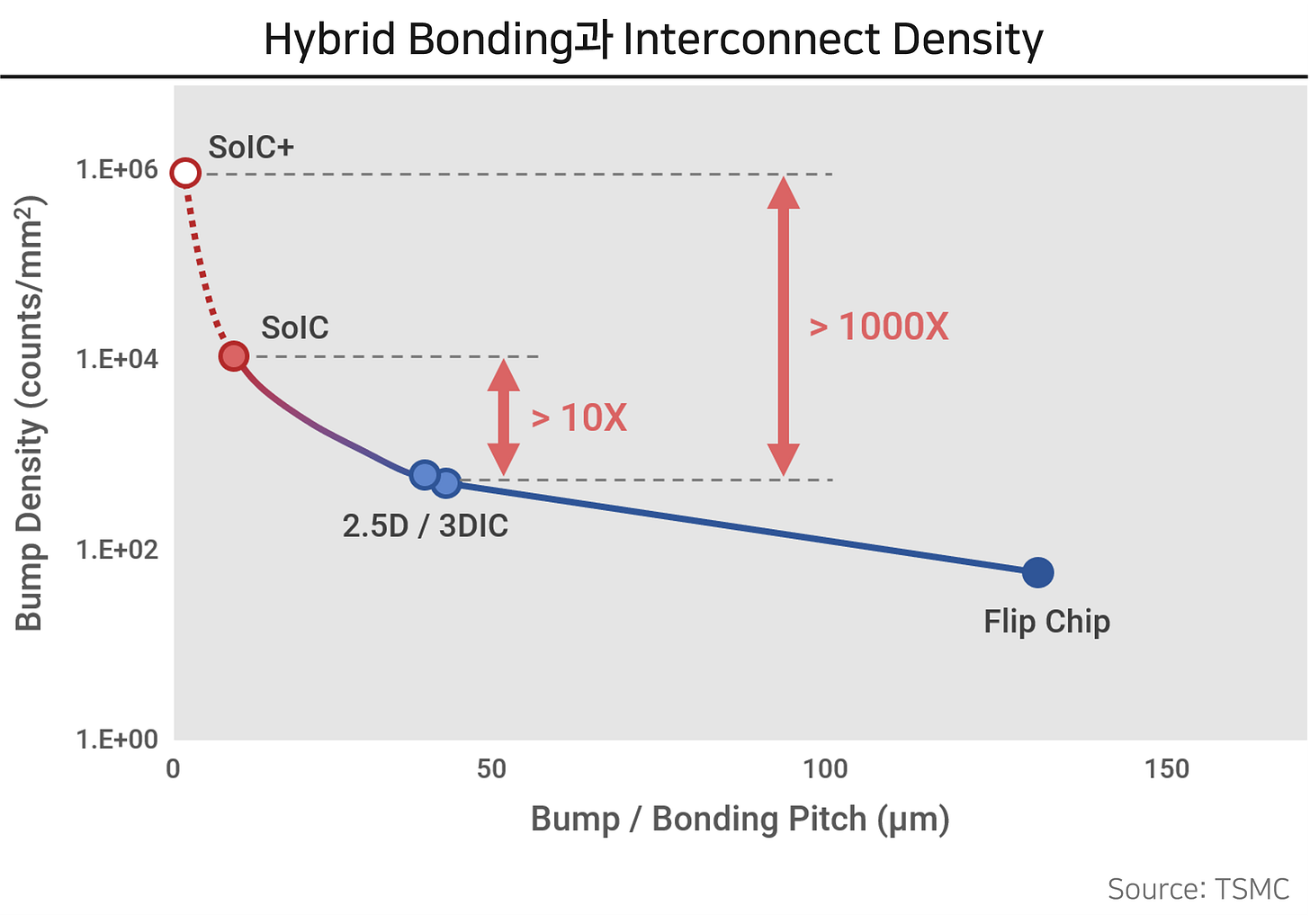

현재 Cu-pillar μbump의 선폭은 약 40μm 수준으로, 낙관적으로 전망해도 1,000개/mm2의 선폭 밀도를 넘기기 힘들 것으로 보입니다. Hybrid bonding이 가능해질 경우 아래 그림과 같이 ~ 1μm 수준의 선폭까지도 확보할 수 있을 것으로 보이고, 이론상 1,000,000개/mm2 이상의 선폭 밀도를 구현할 수 있게 됩니다. HBM으로 고려하자면, 지금보다 1,000배 이상 넓은 bandwidth를 구현할 수 있다는 의미입니다. 이처럼 Hybrid Bonding은 명확한 다음 세대 기술입니다. 과거 Deep UV에서 Extreme UV (EUV)로 변화했던 파운드리 업계의 변화처럼, ‘가능한지 불가능한지 가늠’하는 것이 아니라 ‘생존을 위해 꼭 확보해야 하는’ 기술이라고 보아야 합니다.

Hybrid bonding은 크게 Wafer-to-Wafer (W2W), Die-to-Wafer (D2W) 방법 두 가지로 나뉩니다. 아래 그림처럼 Bottom wafer는 그대로 두되, 위쪽에 쌓을 때 wafer를 통째로 쌓느냐 혹은 die를 잘라서 쌓느냐로 구분됩니다.

결론부터 이야기하자면 W2W는 이미지 센서, 3D NAND에서 활용되어 왔고 High volume manufacturing (HVM) 경험이 있는 기술입니다. 하지만 W2W 기술은 몇몇 한계점을 가지므로 D2W로 기술이 전환되고 있는 상황입니다. 물론 특정 응용 분야에서는 W2W 기술이 지속해서 유지되겠지만, 보다 뛰어난 성능의 컴퓨터를 만들기 위해서는 D2W 기술이 필수적일 것으로 보입니다.

이번 포스팅에서는 먼저 W2W의 공정 프로세스에 대해 설명합니다. 그 다음에는 W2W 공정이 D2W 공정으로 발전하는 과정에서 발생하는 주요 변화 지점을 다루고, 각각의 발전 지점에서 어떤 새로운 기회가 있을지 가늠합니다.

Wafer-to-wafer (W2W)

W2W 기술은 CMOS 이미지 센서에서 상용화된 바 있습니다. Sony는 W2W hybrid bonding을 활용, 3μm 수준의 pitch를 가지는 이미지 센서를 이미 오래 전부터 공급하고 있습니다. NAND 플래시 메모리 개발사 YMTC는 Xtacking이라는 이름으로 2018년부터 W2W hybrid bonding 기술을 활용하고 있습니다. 삼성, 하이닉스도 NAND에서 YMTC의 기술과 유사하게 hybrid bonding을 활용할 계획인 것으로 알려져 있습니다.

W2W 공정은 아래 그림과 같은 프로세스로 진행됩니다. 상세한 내용은 프랑스의 연구소 CEA-Leti에서 실제 공정을 촬영한 영상을 참고하세요.

Hybrid Bonding Interface 형성 (Wafer → CMP)

먼저 Hybrid bonding을 위한 Interface, HBI를 만드는 과정을 거칩니다. Metal bond pad를 형성하고 표면을 매끈하게 갈아냅니다.

Plasma Activationi (Activation)

이후 플라즈마를 통해 표면을 활성화시킵니다. 활성화 단계가 마무리되면, 유전체 표면끼리 화학적으로 끌어당기는 힘이 생기게 됩니다.

Hydration & Cleaning

위 그림에는 표현되지 않았지만 표면을 한 차례 세척하는 과정을 거칩니다. 이는 활성화된 표면에 붙은 불순물을 제거하는 한편, 표면의 활성도를 높이는 역할을 합니다.

Alignment & Bonding (Room temp bonding → Low Temp Batch anneal)

이후 위, 아래 wafer를 정렬하고(alignment), bonding을 진행합니다.

Dicing

Bonding된 wafer를 dicing한 뒤, assembly 과정을 수행합니다.

지금부터는 각각의 process step을 상세히 살펴보며 기존 패키징 공정과 비교해 어떤 변화가 발생하는지 살펴보도록 하겠습니다.

Process 1. Hybrid bonding interfacc (HBI) 형성

HBI 형성 과정은 마지막 CMP 공정의 목적을 제외하면, 기존의 Back-end of line (BEOL) 공정과 거의 동일합니다. 따라서 과학적/기술적으로 큰 변화가 필요한 지점은 아닙니다. 패키징 공정에서 BEOL 공정을 한번 더 추가하므로 소재, 부품, 장비에 대한 수요 증가 측면에서 유의하게 살펴볼 필요가 있습니다. HBI 형성 과정은 아래와 같습니다.

(Process ①) Dielectric layer deposition = 유전체 증착

HBI 형성은 전기가 흐르지 않는 유전체를 증착하는 것부터 시작합니다. 간혹 폴리머를 활용하는 방법도 언급되고 있기는 하지만, throughput과 공정 신뢰성 등에 따라 무기물을 활용하는 것이 표준으로 자리잡을 가능성이 높아 보입니다.

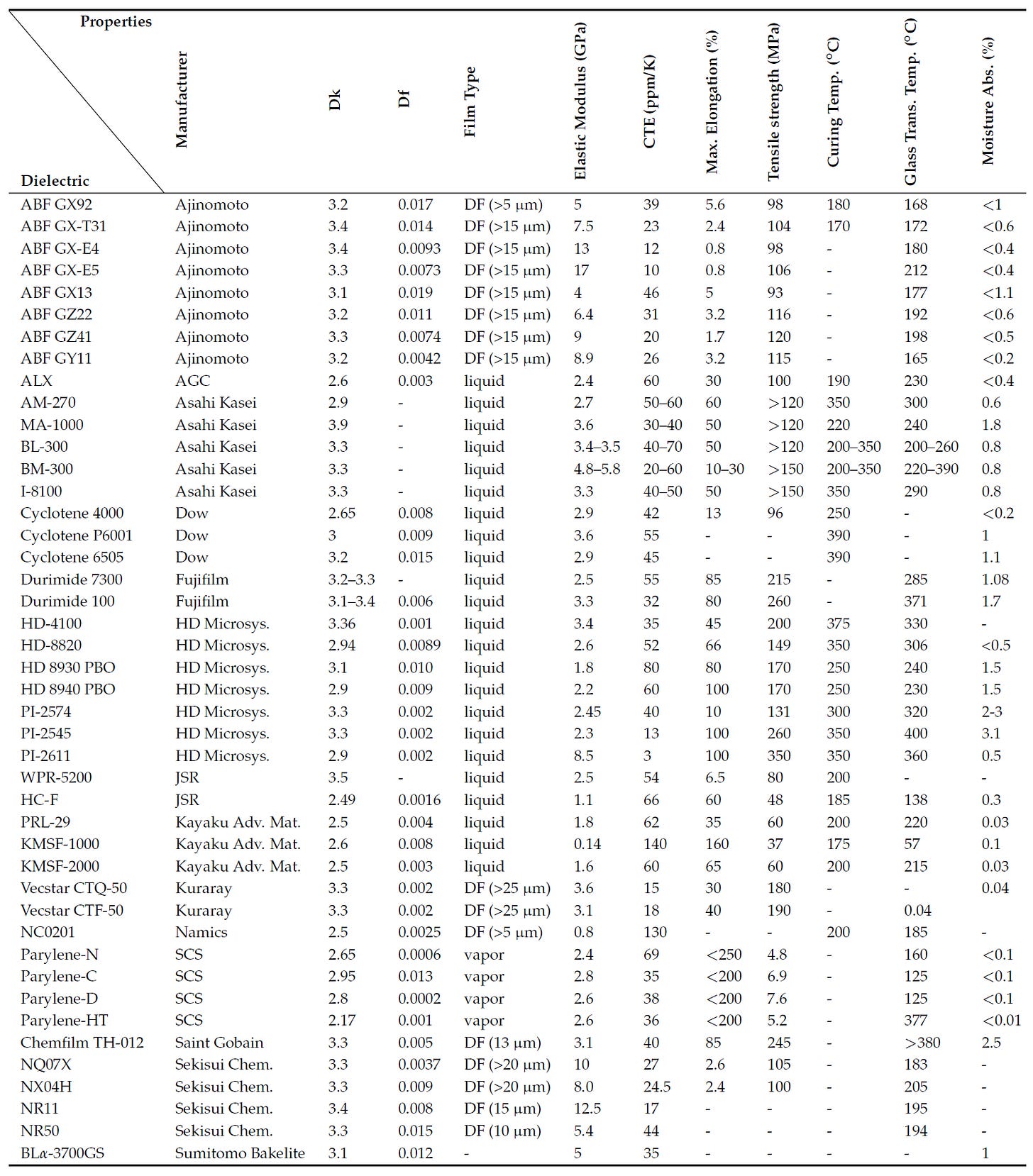

무기물은 SiO2, SiCN, SiON 등이 언급되고 있으며, Plasma-enhanced CVD를 (PECVD) 활용해 증착합니다. 이는 (패키징 공정에 한해) 큰 변화임이 분명한데요. 기존의 패키징 과정에서 활용되었던 유전체 소재는 고체 필름 형태의 Ajinomoto build-up film(ABF)이고, 공정은 고체 필름을 lamination하는 방식으로 준비되었기 때문입니다. 과거에 활용되어 왔던 representative한 유전체 재료는 아래 그림에서 확인할 수 있습니다

다시 돌아와서, 패키징 산업에서 새로이 PECVD 장비가 추가되어야 하는 상황입니다. 기존에 BEOL 공정을 진행했던 foundry 입장에서는 과거 세대에 활용했던 장비를 그대로 활용할 수도 있겠습니다만, OSAT의 경우 PECVD 장비부터 BEOL 생산 라인을 구축할 필요가 생기게 됩니다. 특히 TSMC의 경우 아예 파운드리 BEOL 공정과 HBI 형성 공정을 하나의 라인에서 수행하려는 계획인 것 같습니다. OSAT까지 운반할 필요도 없고, 본인들이 더 잘하는 공정이니 비용, 시간 측면에서 훨씬 유리한 고지를 선점할 수 있겠네요. CapEx에 대한 압박을 받고, 좁은 선폭의 BEOL 공정 경험이 없는 OSAT보다 파운드리의 경쟁력이 강화될 것으로 전망됩니다.

그리고 이 과정은 ‘Plasma-enhanced CVD’입니다. 플라즈마를 활용한다는 것을 꼭 기억해두시길 바랍니다.

(Process ②~④) Lithography to open Cu / PVD / Electroplating

이후 리소그래피/에칭 공정을 통해 Cu pad를 형성할 곳을 패터닝합니다. 이후 PVD를 활용해 Cu seed layer를 증착하고, electroplating 과정을 통해 Cu pad를 형성합니다. 이 과정은 BEOL의 Damascene 공정과 동일하며, SK 하이닉스 뉴스룸의 설명을 공유합니다.

(Process ⑤) Chemical Mechanical Polishing (CMP) for Interface formation

Cu pad에 금속이 자리잡으면, 형성된 HBI를 평탄하게 만들고 적당한 수준의 Cu dishing을 만들기 위해 CMP 공정을 거치게 됩니다.

최근 HBM이 중요해지면서 붉은 색 상자로 표시한 (과정 3) TSV Cu CMP, (과정 9) Passivation CMP & Cu Exposure 과정에서 CMP를 활용하게 된다는 사실이 중요한 투자 포인트로 다루어진 바 있습니다. Hybrid bonding을 적용할 경우 파란 색 상자로 표시한 (과정 5), (과정 10)에서도 CMP 공정이 필요해지게 됩니다. 기존 패키징 공정과 비교해 CMP 공정 과정이 2배 늘어난다는 의미입니다.

특히나 HBI 형성 과정에서는 구리를 갈아내는 CMP가 추가되기 때문에, metal CMP용 슬러리인 SiO2 슬러리 수요가 증가할 것으로 전망됩니다. 마찬가지로 metal CMP용 pad에 대한 수요 역시 증가할 것으로 전망됩니다.

따라서 Hybrid bonding이 상용화되는 과정에서 CMP 관련 소재/부품/장비의 수요 증가는 확정적입니다.

반대로 OSAT/Foundry 업체의 관점에서 보자면, CMP 공정을 잘 잡아내야만 한다는 과제가 떨어지게 됩니다. 확보해야 하는 CMP 공정 내용은 다음과 같습니다:

Roughness

업계에서는 유전체는 0.5nm, 구리 패드는 1nm 수준의 까다로운 roughness 조건을 내세우고 있습니다.

Dishing 조건 확보

Roughness도 문제지만, 이 공정이 ‘예술’의 영역이라고 느끼는 이유는 dishing 조건을 잘 잡아야 하기 때문입니다. Dishing은 아래 그림과 같이 CMP 이후 구리 표면이 아래로 내려앉는 현상을 의미합니다.

Hybrid bonding은 온도를 높일 때 금속이 유전체보다 더 많이 팽창한다는 원리를 활용합니다. Dishing이 너무 심할 경우 금속 사이의 거리가 멀어 결합이 이루어지지 않을 수 있고, Dishing이 충분하지 않다면 Interface 사이로 금속이 흘러나가 Short 발생 원인이 될 수 있습니다.

따라서 적정한 수준의 dishing을 의도적으로 형성시켜야만 합니다. 열처리 온도와 시간에 따라서 적정 수준은 달라지게 되며, 일반적으로 5nm 수준의 미세한 dishing이 필요할 것으로 전망됩니다. 5nm의 미세한 공정 조건을 찾아내는 것이 쉽지 않을 것이 분명합니다.

OSAT/Foundry 기업은 금광을 캐고, CMP 소재/부품/장비 기업들은 곡괭이가 된 격입니다. 그런 의미에서 아래 결론 부분에서 CMP 소재/부품/장비 Value chain을 간단히 정리해두었습니다. ‘Hybrid bonding’이라는 시장 구조 변화에 따라 전반적인 성장을 기대해볼 수 있지만 이들 중에서도 유독 좋은 제품을 만드는 기업에 유의한 투자 기회가 있을 것이라 믿습니다. 관련된 기업들의 valuation multiple, 실적, pure play 여부, 제품 경쟁력 등에 대해서 조만간 통합적으로 정리해 업데이트 하도록 하겠습니다.

Process 2. Plasma activation

형성된 HBI에 높은 에너지의 플라즈마를 조사해 유전체 표면의 특성을 바꾸는 과정입니다.

높은 에너지의 플라즈마에 의해 표면에 형성되어 있던 화학 결합이 일부 해체되고, dangling bond라는게 생기게 됩니다. 위, 아래 Wafer에 모두 동일한 처리를 진행하는데요. 간단히 설명하자면 서로 싸우고 나서 각자 팔짱 끼고 있는 두 찌질한 친구를 데려다 놓고, 힘센 형이 ‘야, 손 잡아’ 하면서 각자의 팔짱을 풀어버리는 과정이라고 보시면 됩니다. 풀린 손끼리 서로 악수하면서 wafer간의 bonding 형성이 가능해지는 것입니다. (엄밀히, 완벽히 맞는 설명은 아니지만 대충 감을 잡기엔 괜찮은 설명일 수 있습니다.)

여기도 최적화의 다툼입니다. 유전체간의 결합력이 강할수록 전체 시스템의 안정성이 증가하기 때문입니다. 가령 W2W hybrid bonding이 마무리된 뒤 dicing 과정을 거치게 되는데요. 이 때 결합 안정성이 충분히 확보되지 못하면 alignment가 깨져버릴 수도 있습니다. 그리고 이러한 문제는 W2W에서 D2W로 기술이 발전하며 더욱 중요해집니다. 그래서 유전체 종류, 플라즈마 종류/세기/온도/시간 등을 최적화하는 것이 중요한 과제가 됩니다.

‘20년 성균관대와 삼성전자에서 수행한 연구에 따르면 SiCN 유전체에 N2 (질소) 플라즈마 처리를 수행하는 것이 강력한 결합을 유도한다고 언급합니다.

‘22년 삼성전자에서 수행한 연구에서는 Plasma 형성 chamber의 기체 분위기에 대해 다룹니다. 내부 기술인지 Plasma 재료가 Gas A, B로 표기되고 있으며, 마찬가지로 초기 유전체간의 결합력을 확보하는 것에 초점을 둡니다.

플라즈마 처리를 하면 유전체에만 영향을 미치는 것이 아니고 Cu pad에도 영향을 미치게 됩니다. Cu-O, Cu-N, Cu-OH 등 다양한 by-product가 형성되며 이들 중 Interconnect의 저항을 크게 증가시키는 물질도 존재합니다. Hybrid bonding을 HBM 등 CMOS 회로에 적용하기 위해서는 저온 조건에서 Bonding을 수행하는 것이 좋은데요, 하필이면 저온 공정에서 이러한 문제가 두드러지게 됩니다. ‘23년 TEL에서 수행한 연구에서는 다양한 플라즈마 조건을 탐색해 저온에서도 활용 가능한 플라즈마 처리 조건을 제안합니다.

다시, 최적화의 다툼은 OSAT/Foundry의 숙명입니다. 생존한 이들에게는 ‘플라즈마’가 필요해집니다. 플라즈마가 두 번째 언급되고 있습니다. OSAT/Foundry가 가장 많이 구매해야 하는 곡괭이가 왠지 플라즈마 제품일 것만 같은.. 묘한 예감이 들기 시작합니다.

Process 3. Hydration & Cleaning

위의 plasma activation 과정이 진행되고 나면, Wafer를 세척하는 과정을 거칩니다. 이 과정은 크게 두 가지 효과를 일으키게 됩니다.

Hydration: 플라즈마 활성화를 통해 유전체 표면이 친수성을 가지게 됩니다. 여기에 물 용매 기반의 용액을 흘려보내면 친수성을 극대화할 수 있습니다.

Cleaning: 동시에 wet cleaning을 수행하면서 표면에 위치한 불순물을 제거하게 됩니다.

아래 그림과 같이 Hybrid bonding 과정에서는 표면의 청결도가 굉장히 중요해집니다.

과거 microbump(μ-bump)를 활용할 때에는 bump와 bump 사이에 공간이 존재했습니다. 따라서 외부에서 유입된 불순 입자가 존재해도 큰 문제가 되지 않았습니다. 하지만 Hybrid bonding에서는 metal pad 사이에 유전체가 위치해 별도의 공간이 없습니다. 따라서, 아주 작은 입자도 Bonding의 퀄리티에 큰 영향을 미칩니다.

‘23년 발표된 마이크론의 논문에서는 “불순 입자는 그의 20배 크기의 공극을 형성할 수 있다”고 언급하고 있습니다. ‘22년 삼성에서는 위 그림과 같이 작은 크기의 입자에 의해 Interconnect에 큰 공극이 형성된다는 연구 결과를 발표합니다.

이런 관점에서 OSAT/Foundry의 구애를 받을 제품 두 가지를 생각해볼 수 있게 됩니다.

수요 증가 1: Wet cleaning 장비(Megasonic 기술)

Megasonic 세척 장비는 세정력이 뛰어나지만 FinFET과 같은 섬세하고 약한 구조에서 활용하기에 너무 강력한 힘을 (세정력을) 가지고 있어 활용되지 못했던 비운의 기술입니다. 오히려 세척에 대한 requirement가 까다롭지 않은 NAND 프로세스에서 제한적으로 활용되어 왔습니다. 하지만 최근 발표되고 있는 ASMPT를 비롯한 장비 업체들, CEA Leti를 비롯한 연구소의 자료를 살펴보면 Hybrid bonding 과정에서 Megasonic 세척을 활용하는 것을 직접적으로 언급하고 있음을 확인할 수 있습니다.

Megasonic 세척 장비를 공급할 수 있는 업체는 중국의 ACM research, 일본의 Tokyo Electron, Screen, 미국의 Lam research 정도가 언급되고 있습니다. 이 중 세척 장비 Pure player는 ACM research 입니다.

이 중 중국의 ACM research는 W2W Hybrid bonding을 3D NAND에 활용하고 있는 YMTC와 함께 Megasonic 세척 기술에 대한 논문을 발표한 바 있습니다. 이 논문에서는 Hybrid bonding 과정에서 Megasonic 세척 기술인 Space Althernating Phase Shift (SAPS)를 활용해 입자를 제거하는 과정을 소개합니다. 세척 소재는 수소 기체와 미량의 암모늄이 함유된 알칼리성 functional water를 활용해 뛰어난 세척 능력을 증명합니다.

첨언하자면, 2019년 발표된 Fraunhofer의 자료에서도 아래 그림과 같이 Hybrid bonding에 적합한 세척 기술로 수소 (Hydrogen peroxide), 암모늄 (Ammonium Peroxide)이 포함된 RCA SC-1 세척을 제안하고 있습니다.

개인적으로는 세척 장비 Pure player인 중국의 ACM research에 매력을 느꼈습니다. 하지만 뒤에서도 언급할 Bonding 장비 업체들인 BESI, ASMPT 등이 자체 세척 모듈을 활용하는 것으로 추정되며 유의한 성장을 기대할 수 있는지 면밀한 확인이 필요한 상황입니다.

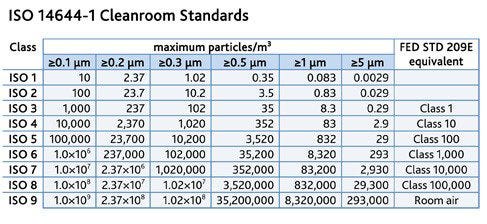

수요 증가 2: 클린룸 장비

추가로 클린룸에 대한 needs가 발생합니다. 업계에서는 통상적으로 ISO class 3 수준을 요구하는 분위기이며 이는 선단 공정 이전 구세대 Foundry Fab과 유사한 수준이라고 볼 수 있습니다. Foundry는 기존에 활용하던 Fab을 활용할 수 있지만, OSAT 업체들의 경우 지금까지 이 정도로 까다로운 요구가 없었기에 설비 투자를 강요받는 상황이 됩니다.

이런 상황에 따라 Bonding 장비 업체들은 자신들의 장비에 클린룸 장치를 추가하여 판매하기 시작합니다. 작은 Unit마다 하나의 클린룸 장비가 활용되는 상황이 되면서 클린룸 부품/장비 기업의 성장을 기대해볼 수 있게 됩니다.

Process 4. Alignment & bonding

실상 이 과정이 가장 어렵고 ‘Hybrid bonding 상용화의 핵심’이라고 볼 수 있습니다. 장비의 성능 지표는 (1) 정확성, (2) 속도입니다. 다만 W2W bonding은 한 번의 align을 통해 수십개의 chip bonding이 수행되기 때문에 상대적으로 속도보다 정확성을 확보하는 것이 중요합니다.

현재 W2W hybrid bonding의 Alignment/Bonding 장비 시장은 3개 정도의 기업이 과점하고 있습니다. 1위 오스트리아 EV Group (EVG, ~80%), 2위 일본 Tokyo Electron (TEL, ~15%, TSMC 공급), 3위 독일 SUSS 세 기업이 시장을 지배하고 있습니다. EVG는 비상장 기업이고, TEL은 Pure play라기엔 사업 포트폴리오가 너무 넓습니다. SUSS 역시 temporary bonding 장비가 주된 사업 영역이고, 10대 미만의 공급 record를 가진 것으로 확인됩니다. 중요한 시장임은 분명한데 관련한 투자 포인트로 투자할만한 기업은 보이지 않습니다.

EVG가 시장을 지배하고 있으며, SmartView system 특허를 통해 기술적으로 높은 장벽을 유지하고 있습니다. 앞단의 HBI formation/activation까지 turnkey로 공급한다는 점도 주목할만 합니다. 주로 Image sensor, NAND 기업들에게 공급해왔던 것으로 보입니다. 최근에는 Direct D2W와 W2W의 중간 단계인 Collective D2W의 중요성에 대해 언급하며 product line을 확대하고 있습니다. Direct D2W 장비는 ASMPT와 함께 개발하고 있는 것으로 확인됩니다. EVG는 앞단의 HBI formation/activation/temporary bonding 장비를, ASMPT는 align system을 개발합니다. D2W에 대한 내용은 다가올 섹션에서 자세히 다루도록 하겠습니다.

TEL은 ‘19년부터 꾸준히 TSMC의 Excellent Performance Award를 수상하고 있으며, 관련된 전반적인 매출 발생이 TSMC향일 것으로 예상됩니다. TSMC는 Graphcore IPU를 W2W Hybrid bonding 기술로, AMD V-cache를 Collective D2W Hybrid bonding 기술로 생산하면서 Logic에 Hybrid bonding을 도입하고 있습니다. 향후 TSMC의 Hybrid Bonding 도입 확대에 따라 M/S 확대 가능성도 존재합니다.

마지막 후발 주자는 SUSS microsystem입니다만, 거의 판매되지 않는 것으로 보입니다. 마찬가지로 프랑스의 SES와 협력해 Direct D2W 장비를 개발 중인 것으로 확인됩니다. SUSS microsystem의 경우 Temporary bonding 장비를 주력 제품으로 하고 있으며, 얇은 wafer/die를 handling하기 위해 꼭 필요한 기술입니다. 최근 HBM 등이 중요하게 조명되며 SUSS도 함께 관심을 받고 있는 상황으로 보입니다. W2W bonding 장비로 투자 포인트를 설명하기에는 유효하지 않다고 판단됩니다.

Process 5. Dicing

사실상 Bonding이 마무리된 뒤에 dicing하므로, contaminant 문제에서 자유롭습니다. 하지만 Wafer를 샌드위치처럼 포개기 때문에, 어디부터 어디까지 잘라야 하는지 확인하기 어렵습니다 (Face-to-Face bonding에 한정). 기존에 위치 정보를 입력해두고 별도의 광학적 피드백 없이 dicing을 수행해야 할 것으로 보이는데요. 정확한 기계적 제어가 중요한 기술이 될 것이라고 생각됩니다. 아직까지 Dicing 장비 관련 기업들에 대해서는 상세히 살펴보지 못했으므로, 이번 포스팅에서는 자세히 설명하지 않습니다.

정리: Key Momentum & Limitation & Supply chain landscape

현황

W2W hybrid bonding은 이미 몇몇 응용 분야에서 High volume manufacturing (HVM)에 적용되고 있습니다. 대표적인 분야는 이미지 센서, 3D NAND입니다.

Hybrid bonding이라는 새로운 기술이 도입되는 과정에서 CMP, Megasonic 세척, 클린룸, 플라즈마, Dicing으로 대표되는, ‘금광의 곡괭이’ 격 제품들이 우수수 쏟아집니다. 프로세스 전반을 살펴볼 때 (1) 플라즈마 관련 제품들의 수요가 가장 급격히 증가할 것이고, (2) Dicing/CMP의 경우 높은 수준의 품질을 가지는 기업들에서 큰 부가가치가 발생할 것으로 보입니다. 그리고 해당 value chain은 D2W 기술에서도 역시 활용되므로, 위의 아이디어는 D2W 기술 개발 과정에서도 유효합니다.

향후 시장 확장성

EVG에서는 아래 그림과 같이 W2W hybrid bonding에 대한 낙관적인 전망을 내놓고 있습니다. 하지만 개인적으로 W2W hybrid bonding은 이미지 센서, NAND, DDR6+(3D DRAM), 그리고 일부 차세대 메모리 분야까지가 한계 지점일 것이라고 생각합니다. 다른 시장의 경우 ‘Known Good Die (KGD)’ 구현에 적합하지 않은 W2W 기법을 활용하기 어렵다는 판단입니다.

Momentum 1 = 3D NAND:

3D NAND는 기존에 좌-우로 붙어있던 메모리 셀과 구동 CMOS를 위-아래로 적층하는 기술이며, 이를 통해 같은 면적에 2배의 메모리를 배치할 수 있게 됩니다. YMTC에서 Xtacking이라는 브랜드로 3D NAND 제품을 생산하고 있으며, 조만간 일본의 키옥시아, 우리나라 하이닉스/삼성 역시 Hybrid bonding 기반의 3D NAND를 출시할 것으로 보입니다. 상용화에 필요한 기술은 모두 갖추고 있으나 아직은 M/S가 작은 상황이고, 혁신적으로 메모리 용량을 늘릴 수 있습니다. 시장 확대를 위한 모든 조건을 갖춘 상태입니다.

Momentum 2 = 3D DRAM:

SK 하이닉스에서 3D DRAM에 W2W hybrid bonding 적용 방법을 연구하고 있는 것으로 확인됩니다. 3D NAND와 유사하게 메모리 셀과 구동 CMOS를 위-아래로 적층하겠다는 관점의 기술인데요. DRAM은 NAND 대비 더 높은 트랜지스터 성능이 필요하기 때문에, 단순 CVD가 아닌 Epitaxy 등 높은 원가의 제조 공정이 필요했기 때문에 아직까지 상용화되지 못했습니다. 만약 W2W Hybrid bonding이 가능해진다면 Wafer 각각에 DRAM layer를 만든 뒤, Hybrid bonding을 활용해 접합하는 방법으로 해결이 가능합니다. 다음 세대 DRAM을 위해 꼭 필요한 기술이 될 가능성이 있습니다.

Momentum 3 = micro LED:

W2W hybrid bonding은 가장 높은 Interconnect 밀도를 구현할 수 있는 기술일 것으로 전망됩니다. ‘23년 12월 발표된 벨기에의 반도체 연구소 imec의 연구에서는 Cu pad의 공간 배치를 사각형에서 육각형 형태로 바꾸고, Top wafer의 pad를 bottom wafer 대비 더 작게 디자인해 400nm의 pitch(!)를 가지는 극도로 미세한 수준의 W2W hybrid bonding에 성공하였습니다. 참고로, 이 연구는 EVG 장비를 활용하였습니다. 개인적으로는 아직까지 개화되지 않은 MicroLED 시장에서 이 같은 W2W hybrid bonding이 아주 큰 역할을 할 수 있을 것으로 생각됩니다. III-V 반도체로 400nm 수준의 작은 픽셀을 구현하고, 이를 구동 회로와 hybrid bonding하게 된다면 무려 65,000 ppi 이상의 높은 해상도를 구현할 수 있습니다. 향후 몰입감 높은 XR 구현을 위한 충분한 기술 스펙이 될 것이라고 생각합니다.

한계점

쌓으면서 잘못된 die를 걸러낼 수가 없습니다. 앞선 포스팅에서 언급했던 Known Good Dies (KGD) 공정이 불가능합니다. 열 개의 층을 쌓았을 때 한 층의 die라도 잘못되면 10개의 die를 모두 버려야 합니다. 한 장의 wafer에서 90%의 수율을 가질 때, 10층을 쌓는다면 수율은 35% 수준으로 감소합니다. 따라서 HBM처럼 10개 이상의 층을 쌓을 때 W2W hybrid bonding을 활용하게 되면 극악의 수율을 맛보게 될 가능성이 높습니다.

두 번째는 Heterogeneous integration이 어렵다는 점입니다. W2W hybrid bonding에서는 top wafer와 bottom wafer에 형성된 die의 크기가 동일해야 합니다. 여러 다른 die를 heterogenous integration하는 것이 중요해진 만큼, W2W는 그 확장성에서 한계를 가집니다.

이러한 이유로 D2W 기술이 중요하게 highlight되기 시작합니다.

Collective Die-to-Wafer (Co-D2W)

앞서 언급한 바와 같이 W2W는 KGD 공정이 불가능합니다. 그런 의미에서 Top wafer에서 성능이 확인된 die만을 잘라 이를 temporary carrier에 옮겨붙인 뒤, 성능이 확인된 Bottom wafer die에 붙이는 Co-D2W 방식이 언급되기 시작합니다. 2018년 EVG에서 Gemini for Co-D2W 장비를 출시하면서 시장이 개화된 것으로 보입니다.

Co-D2W의 공정 프로세스는 아래 그림과 같습니다. 전반적으로 W2W 방식을 따르지만 (1) Dicing 과정과 Carrier population 과정, (2) Carrier separation 과정이 추가됩니다.

산업에서는 AMD가 TSMC를 통해 공급했던 V-cache가 유일한 Co-D2W HVM 사례로 확인됩니다. AMD V-cahce는 9μm의 Interconnect pitch를 가집니다. AMD는 hybrid bonding을 도입하며 Interconnect의 에너지 효율을 3배, Interconnect 밀도를 15배 이상 증가시키는 데 성공했다고 강조하고 있습니다. 아직까지 Hybrid bonding 공정이 최적화되지 않았음에도 Bandwidth가 10배 이상 증가합니다. Hybrid bonding이 얼마나 큰 파급력을 가지는지 조금씩 느껴지는 부분입니다.

Intel에서도 Quasi Monolithic Chip (QMC)이라는 개념을 구현하기 위해 Collective D2W 방식을 활용하고 있습니다. 이번 포스팅에서는 QMC는 자세히 다루지 않고, 관련한 Intel의 발표 영상을 공유하도록 하겠습니다.

Key Difference 1. Wafer dicinig

성능 테스트 이후 KGD만을 활용하려면 Wafer dicing을 통해 성능 테스트를 통과한 die를 잘라내는 과정이 필수적입니다. 아래 그림에서는 Plasma dicing 기술을 활용한 dicing 과정을 상세히 표현합니다.

Carrier wafer bonding:

형성된 HBI층에 불순물이 발생하는 것을 최소화하기 위한 Protection layer를 코팅한 뒤, carrier substrate에 HBI 방향이 맞닿도록 wafer를 붙입니다.

Backgrinding & CMP:

뒷면을 얇고 평탄하게 갈아줍니다. 두께를 얇게 만들어야 dicing 과정을 매끄럽게 진행할 수 있으며, 이 때 높은 평탄도를 확보해야 Hybrid bonding 과정에 방해되지 않습니다.

Patterning:

리소그래피 공정을 통해 Dicing할 부분만을 드러냅니다.

Plasma dicing (Dicing with Reactive Ion Etching - RIE):

반도체 전공정에서 활용되었던 RIE 공정을 활용해 Die 사이의 공간을 깎아냅니다. 이 때 플라즈마가 활용됩니다.

Delaminate from carrier → Pick & Place to carrier wafer (이 과정은 아래에서 다시 설명)

이제 잘라낸 die를 다른 carrier wafer에 align하여 붙입니다. 이때는 HBI 반대쪽, 즉 DIE 뒤쪽이 Carrier와 맞닿도록 붙입니다. 이 과정은 아래에서 보다 상세히 다루겠습니다.

Dicing 방법은 크게 Blade, Laser, Plasma dicing 세 가지 기술로 나뉩니다. 지금까지는 Blade/Laser dicing 기술이 주로 활용되어 왔지만, 앞서 언급한대로 Hybrid bonding 과정은 여러 모로 까다로워지면서 Plasma dicing으로 전환될 것이라고 판단됩니다. 그 이유를 크게 세 가지 꼭지에서 설명합니다.

Contaminant 최소화:

앞선 섹션에서 언급한 것과 같이, Hybrid bonding에서는 아주 작은 수준의 불순 입자도 허용되지 않습니다. Blade/Laser dicing을 활용하면 굉장히 많은 양의 불순 입자가 발생합니다. 아래 그림은 Laser stealth dicing 과정을 거치며 불순 입자가 7배 증가한다는 Micron의 연구 내용입니다.

Micron은 이러한 Contamination 문제를 해결하기 위해 Plasma dicing을 도입해야 한다고 주장합니다. 그럼에도 이 연구에서는 dicing 속도의 문제로 Laser groove patterning을 함께 활용하는데요. 애석하게도 Laser grooving 역시 꽤 많은 불순 입자를 형성하기 때문에 별도의 세척 과정을 추가합니다. 이런 이유로, 저는 궁극적으로 모든 Dicing 장비가 Plasma dicing 장비로 전환될 것이라고 생각합니다.

Chipping 혹은 mechanical distortion 최소화:

Hybrid bonding에서는 표면의 평탄도를 강조하고, 장비와 die 뒷면이 접착한 채로 align을 진행하므로 뒷면의 평탄도 역시 굉장히 중요합니다. Blade/Laser dicing에서는 Wafer에 필연적인 기계적 스트레스가 발생하게 됩니다. 이는 die 뒷면 혹은 측면에 Warping, chippping을 유도하게 됩니다. 반대로 Plasma dicing에서는 기계적 스트레스 없이 Dicing이 진행되고, 휨이나 Chipping 없이 깨끗한 Dicing을 수행할 수 있습니다. 따라서 Plasma dicing을 활용하는 것이 이상적입니다.

공정 속도 (Throughput):

Blade/Laser dicing은 잘려지는 각 지점을 훑고 지나가는 ‘Scan’ 방식이라면, Plasma dicing은 모든 지점을 동시에 잘라낼 수 있는 방식입니다. 따라서 각 wafer를 잘라내는 데 필요한 시간이 감소하게 됩니다.

이러한 이유로 인해, 결과적으로 Plasma dicing이 시장을 점차 지배해갈 것이라고 생각합니다. Plasma dicing의 프로세스에 대해 조금 더 자세히 궁금하신 분들은 다음 영상을 참고하시는 것을 추천합니다.

Plasma dicing 장비는 일본의 Disco, Panasonic, Samco, 미국의 KLA, Plasma-Therm 등의 장비 회사가 제조하고 있습니다. 더하여, 원리상 Plasma dicing은 반도체 식각 공정과 동일한 Reactive Ion Etching 방식을 활용하기 때문에 기존의 식각 장비 기업들도 충분히 진출할 수 있는 시장이라고 생각됩니다. 저는 Dicing 장비 pure player인 일본의 Disco를 매력적이라고 생각하고 있으나, 조금 더 면밀한 조사가 필요합니다.

Plasma dicing 과정에서는 기존의 식각 공정보다 훨씬 두꺼운 실리콘 Wafer를 깎아내야 하는 과제에 당면합니다. 충분한 속도까지 확보하기 위해서는 높은 에너지의 플라즈마를 활용해야 합니다. 이에 따라 기존 식각 공정보다 더 빠른 속도로 부품이 소모됩니다. 대표적으로는 플라즈마 처리 과정에서 웨이퍼를 잡아주는 Focusing ring이 있겠습니다.

여기서 다시 강조할 것은 ‘플라즈마’입니다. 전체 공정에서 벌써 세 번째 - PECVD, Plasma activation, Plasma dicing - 언급되고 있습니다. 저는 세 개의 다른 공정 모두에서 활용될 수 있는 중요 부품에 눈길이 갑니다. 대표적으로는 플라즈마를 생성하는 플라즈마 생성기(Generator)가 있겠습니다.

정리하자면, Dicing 과정에서 Contaminant를 최소화하기 위한 기술로 Plasma dicing이 조명받고 있습니다. 아직까지 패키징 공정에서 침투율이 낮기에 Plasma dicing 장비 기업의 성장이 기대되고, Plasma dicing의 특성상 기존 식각 공정 대비 소모품 교체 주기가 짧아지면서 관련 기업들 역시 유의한 성장을 기대할 수 있을 것으로 기대됩니다. 마지막으로 계속해서 언급되는 ‘플라즈마’ 관련 공정 모두에 활용될 수 있는 플라즈마 생성기와 같은 value chain에 큰 수혜가 있을 것으로 보입니다.

Key Difference 2. Carrier wafer population, Alignment, Separation

이제 dicing 된 die를 새로운 wafer 위에 bonding시켜야 합니다. 아래 그림에서는 Dicing 이후부터 Bonding이 완료되기까지의 과정을 소개합니다.

Carrier Substrate에 Pick & Align (Collect 과정, Carrier Population 과정):

잘라진 die를 carrier에 옮기는 과정입니다. Carrier substrate에는 아래 그림과 같이 리소그래피 공정을 통해 미리 만들어진 지도가 있고, Die를 그 위에 Align하여 배치하게 됩니다.

Carrier에 Die가 잔뜩 올라가기 때문에 Carrier population 과정이라고 부르기도 합니다. Co-D2W의 가장 핵심적인 과정인데요. 직접 Target wafer에 Die를 올리지 않기 때문에 다음과 같은 장점이 생기게 됩니다.

Carrier에는 임시 접착제가 발라져 있어, Die를 정렬한 뒤 내려놓으면 그 자리에 고정되게 됩니다. 임시 접착은 HBI와 반대 방향으로 진행되므로 Die를 배치한 뒤 마음에 들지 않으면 언제든지 정렬을 재정비할 수 있게 됩니다.

Carrier population 과정 이후에 플라즈마 활성화 및 표면 세척 단계를 거치게 됩니다. 이에 따라 Hybrid bonding의 중요한 조건 중 하나인 표면 청결도 확보가 용이해집니다.

각각의 Die를 배치할 때 Hybrid bonding을 형성하지 않습니다. 따라서 전체 공정 속도가 빨라지는데요. 관련해서는 Direct D2W 기술에 대해 설명하며 좀 더 자세히 비교합니다.

Protection layer 삭제 및 Plasma activation:

Dicing과 Pick & Align 과정에서도 매끄러운 HBI를 유지하기 위해 증착해둔 Protection layer를 지웁니다. 이후 플라즈마 활성화 및 표면 세척 단계를 진행합니다. 이 과정은 W2W와 동일합니다.

W2W align & bonding:

이후 W2W align과 bonding 과정을 진행하며, 이 역시 기존 W2W 공정과 동일합니다. 첨언하자면 전체 프로세스에 align 과정이 두 번 진행됩니다 (Carrier population, W2W align). 당연히 align을 한 차례만 진행할 때보다 오류가 누적되므로 정확도가 떨어지게 됩니다. 따라서 아래 그림과 같이 Co-D2W는 W2W 공정이 구현하는 pitch를 절대로 뛰어넘을 수 없습니다. Co-D2W 기술이 가지는 태생적인 한계점입니다.

Carrier substrate delamination:

마지막으로 불필요한 Carrier substrate를 떼어내야 합니다. 그냥 무턱대고 힘으로 뜯어내면 열심히 만들어둔 Hybrid bonding이 망가지므로, Bonding interface에 영향을 주지 않으면서도 Die에 불순물이 남지 않도록 깔끔하게 떨어뜨릴 기술이 필요합니다. 이처럼, Carrier에 임시로 Die를 붙이고 이를 떨어뜨리는 과정을 “Temporary bond debond (TBDB)” 기술이라고 이야기합니다.

Temporary bonding 장비를 가장 잘 만드는 기업이 앞서 언급했던 SUSS입니다. ‘20년, SUSS는 미국의 비상장사 Brewer science, 벨기에의 imec과 함께 Laser release layer (LRL) 기반의 TBDB 시스템을 제안합니다. 하지만 LRL을 활용할 경우 Laser를 조사하는 과정에서 Die에 불필요한 기계적/열적 에너지가 가해지게 됩니다. 이를 해결하기 위해 ‘21년, ‘22년 차례로 ‘Acoustic layer’를 추가하는 방식을 제안합니다. 모든 소재는 Brewer science의 Temporary bonding 소재를 활용하고 있습니다. 이 정도의 공고한 협력 관계라면, SUSS의 Temporary bonding 장비 수요가 증가하면서 Brewer Science 소재에 대한 수요도 함께 증가할 수 있겠습니다.

반대로 앞서 언급했던 Dicing 장비 기업 Disco에서는 아주 얇은 SiO2 막을 Temporary bonding 소재로 활용하자는 아이디어를 제안합니다. 대부분 Temporary bonding은 고분자 소재를 활용하는데, 독특하게 무기물을 제안하고 있습니다.

몇몇 연구들을 살펴보았지만, 전체 landscape와 소재의 조성에 대한 내용까지 깊게 공부하지는 못했습니다. 중요한 점은 기존의 Thermocompression Bonding과 비교해 기본적으로 더 완벽한 접착/탈착 기능을 요구한다는 것입니다. (관련 내용은 이 포스팅에 조용히 업데이트 해두겠습니다.)

정리: Key Momentum & Limitation & Supply chain landscape

현황

Co-D2W 기술은 AMD의 V-cache를 통해 세상에 첫 발을 내딛었습니다. DRAM 메모리보다 Logic에서 Hybrid bonding이 먼저 활용되었다는 점도 꽤나 상징적입니다. AMD V-cache에 활용된 interconnect pitch는 9μm 수준으로 밝혀졌고, 이를 통해 기존 대비 Interconnect 숫자를 15배 이상 늘리는 데 성공했습니다.

몇몇 기업에서 R&D를 지속하고 있는 것으로 확인되지만 Mainstream의 위용을 보여주고 있지는 못하다고 생각합니다. 태생적으로 가지고 있는 정확도에서의 한계로 인해 큰 관심을 받고 있지 못한 모양새입니다. 그 한계점은 다음과 같습니다:

한계점

Align 과정을 두 번 거치기 때문에 정확도에 대한 태생적 한계가 분명히 존재합니다. 또 Carrier populuation 과정에서 기본적으로 두께가 일정하지 않은 접착 소재를 붙인 채 Pick & Align을 하기 때문에 여기서 오는 정확도의 문제도 무시할 수 없습니다.

결과적으로 Logic, Memory 할 것 없이 모두 더 많은 층을 쌓는 기술로 향하고 있습니다. 하지만 Co-D2W의 경우 부착되는 Die 뒷면에 Temporary bonding 접착제를 항상 제거해야 하기 때문에 더 많은 시간이 필요해지게 되고, 보다 까다로운 세척 기술을 추가로 개발해야만 합니다.

좌-우의 Align 정확도의 한계에 더해 상-하의 표면 평탄도까지 한계가 명확합니다. 언젠가는 천장을 맞이할 수 밖에 없는 기술에 대해 과감하게 투자하기는 어려울 것이라고 생각합니다.

향후 시장 확장성 = Di-D2W의 중간 단계로서 주로 활용될 것으로 판단

3μm보다 큰 interconnect pitch를 가지는 package: 정확도의 태생적 한계로 높은 수준의 Interconnect pitch를 구현하기 어려울 것이라고 생각합니다.

2-layer logic 디바이스: Multi-layer Logic으로 넘어가기 전, 중간 단계에서 AMD V-cache와 비슷한 방식의 2-layer Logic에서 활용될 수 있습니다.

Direct Die-to-Wafer (Di-D2W)

Di-D2W 공정은 아래 그림과 같이 마지막에 Die를 하나씩 pick-up 해서 bottom wafer에 직접 align 시키게 됩니다. 다른 공정들은 Co-D2W 공정과 동일하게 진행됩니다. 조금 더 쉬운 이해를 돕기 위해 CEA-Leti에서 촬영한 영상을 공유합니다.

아직까지 Di-D2W는 상용화에 성공한 적이 없습니다. 하지만 앞서 언급한대로 W2W의 경우 수율 문제로, Co-D2W의 경우 속도 문제로 여러 개의 층을 쌓아 올리기는 어렵고, 두번의 alignment 과정을 거치면서 정확도가 점점 떨어지게 됩니다. 따라서 여러 층의 다른 die를 쌓아올리는 3D Chip 구현을 위해 Di-D2W Hybrid bonding 기술은 필수적으로 개발되어야만 합니다.

이러한 관점에 따라 3D stack이 이미 중요하게 적용되는 HBM 개발사들이 Di-D2W Hybrid bonding 개발에 집중하고 있는 것으로 확인됩니다. SK 하이닉스, Micron은 Di-D2W 특허 DBI Ultra를 개발한 Adeia와 라이선스 계약을 체결했고, 삼성전자는 올해 2월 BESI와 Applied Materials가 공동 개발한 Di-D2W 장비를 구매하였습니다.

Di-D2W alignment/bonding 장비가 일상적으로 활용되기 시작하면, 지금보다 100배 이상 높은 Interconnect density를 가지는 3D stack die를 생산할 수 있게 됩니다. 3D stack die가 가능해지면서 아래 그림과 같이 시스템 반도체 설계에서도 패러다임 변화가 생깁니다. 이런 측면에서 저는 조금 과장 보태자면 Di-D2W 기술이 패키징 시장에 만들 기술적 파급력은 EUV 기술이 Foundry 시장에 만들었던 파급력 만큼이나 강력할 것이라고 생각합니다.

설계에 미치는 영향까지 고려하면 Di-D2W 적층 기술 개발에 성공할 경우, HBM 시장에서의 헤게모니를 확보함과 동시에 Foundry 영업력도 확보될 가능성이 높습니다. HBM 시장의 헤게모니, Foundry 영업력이라는 거대한 파급력인 만큼 삼성과 하이닉스가 꼭.. Di-D2W를 구현하는 리더가 되기를 염원합니다.

Key difference: Direct Pick & Place with precise alignment

사실 기술에 대한 설명은 간단합니다. 준비된 Die를 잡아서, Wafer 위의 적당한 위치에 올려두면 됩니다. 설명만큼 구현이 간단하지 않다는 것이 문제입니다. 구현 난이도가 높은 이유는 다음과 같습니다:

Align이 완료됨과 동시에 bonding 수행

W2W 기술의 경우, Alignment를 진행한 뒤 두 wafer를 바로 포개지 않습니다. 간격을 유지한 채로 높은 수준의 진공도를 가진 bonding chamber로 이동해 bonding을 진행합니다. 이 과정을 통해 표면의 불순물을 한차례 더 제거할 수 있게 됩니다.

Co-D2W 기술의 경우 우선 Carrier에 임시 align을 하기 때문에, Carrier에 부착한 뒤 다시 점검하며 die 위치를 세부적으로 재조정할 수 있습니다. 마찬가지로 W2W 기술을 활용하기 때문에 alignment 과정과 bonding이 분리되어 청결도 측면에서도 강점을 가집니다.

Di-D2W의 경우 die 하나를 align할 때마다 bonding chamber에 다녀오기엔 시간이 너무 오래 걸립니다. 따라서 align이 완료됨과 동시에 bonding을 수행하는데요. Pick-and-Place 과정에서 발생한 불순물을 별도의 고진공으로 제거해줄 수 없게 되고, 잘못 align을 했을 때에도 세부 재조정을 할 수 없게 됩니다.

유전체 간의 결합력이 약하면, 다른 die를 bonding하는 과정에서 생기는 미세한 기계적 스트레스로 인해 align이 틀어질 수도 있습니다. 이에 따라 접착력이 좋은 dielectric film과 plasma 처리 조건 확보에 대한 중요성도 더욱 강조되게 됩니다.

느린 속도

딤섬 판을 쌓아올리는 시나리오를 생각해보겠습니다. 각 판에는 딤섬이 6개 들어 있다고 가정해보겠습니다.

(W2W) 딤섬 6개가 들어 있는 판을 그대로 쪄서 이전 판 위에 올립니다.

(Co-D2W) 6개 딤섬 중 예쁘게 만들어진 4개를 하나의 다른 판에 옮겨 찐 다음, 그 판을 이전 판 위에 올립니다.

(Di-D2W) 예쁘게 만들어진 4개의 딤섬을 하나씩 순서대로 찐 뒤에 이전 판 위에 하나씩 올립니다.

물론 엄밀히 맞는 설명은 아니겠습니다만, Di-D2W 방식이 가장 느릴 것임이 분명해 보입니다. 딤섬은 6개 뿐이지만, 한 개의 Wafer는 Die를 수십 개 포함하고 있으므로.. 속도 차이에 의한 생산성 저하는 분명 큰 문제가 됩니다.

속도 문제에 따른 정확도 확보 난이도

기존 Thermocompression bonding의 경우 정확도 수준이 2~3um 수준이었지만, Interconnect pitch가 작은 Hybrid bonding의 경우 200nm 수준의 훨씬 더 까다로운 정확도를 요구합니다. 실제로 EVG의 W2W hybrid bonder의 정확도는 50nm 수준이며 이를 활용해 벨기에의 반도체 연구소 imec이 400nm pitch를 구현하는데 성공한 바 있습니다. 이처럼, pitch가 미세해지며 기본적으로 요구하는 정확도의 수준이 높아집니다.

100개의 die를 1초에 1개씩 align할 때보다 100개의 die가 위치한 wafer를 50초 동안 align하는 것이 공정의 전체 속도 상으로는 훨씬 빠릅니다. W2W 기술에서는 50초 동안 align해서 50nm의 정확도를 확보하는 데 성공했다면, Di-D2W 기술에서는 1초 동안 150~200nm 수준의 정확도를 확보해야 합니다. 듣기만 해도 어렵습니다.

이런 이유들로 인해 아직까지 상용화된 Di-D2W 사례는 없습니다. 따라서 이 난이도 높은 장비를 개발하는 데 성공하면 시장 개화의 과실을 누리는 동시에 깊은 기술적 해자를 확보할 수 있을 것으로 보입니다.

성능 측면에서의 변화 뿐만 아니라, Di-D2W 기술의 도입은 Bonding 장비의 Price/Quantity 모두 증가하는 트렌드를 만들게 됩니다.

Price 증가:

Hybrid bonding 장비는 현재 가장 발전된 기술인 Thermocompression Bonder보다 가격이 3~5배 사이에 형성되고 있습니다.

Quantity 증가:

Hybrid bonding은 μbump 대비 두께가 얇습니다. 아래 그림과 같이 같은 높이에 더 많은 층을 쌓을 수 있게 됩니다. 더 많은 층을 쌓으려면 더 많은 Bonding을 형성해야 합니다.

Chiplet design이 활성화되면서 이전에는 하나로 통합되어 있던 chip이 나뉘게 되고, 이들을 연결하기 위해 bonding 숫자가 증가하게 됩니다. (사실 이러한 변화는 모든 Bonding 기술에 대해 동일하게 적용됩니다. 아직 남아있는 한미반도체의 모멘텀일수도..)

Di-D2W 장비는 기존 TCB 장비보다 6배 느립니다. 그런데 형성해야 하는 Bonding 개수는 증가합니다. 따라서 그만큼 더 많은 장비 구매 수요가 생길 가능성이 높습니다. 이러한 가정은 수천만원을 호가하는 nVIDIA 시스템을 구매하기 위해 지금도 빼곡히 사람들이 기다리고 있기 때문입니다. 분명 공정 비용은 증가하겠지만, 거기에서 오는 성능 변화가 혁신적이라면 기업들은 주저하지 않고 투자할 분위기입니다.

Di-D2W 장비를 개발할 수 있는 기업은 기존의 Die bonder (혹은 Die attch) 업체로 좁혀집니다. 2019년 기준, Die bonder 업체의 Market share는 아래와 같습니다. 당시에는 네덜란드의 BESI, 홍콩의 ASMPT 두 기업이 60%를 점유하고 있습니다. 이 데이터를 발표한 Yole의 보고서에서는 두 기업만이 Die attch 장비에 몰두하는 pure player라고 소개합니다. BESI의 경우 정확도 7um 이하의 첨단 die bonder에서 70% 이상의 시장 점유율을 확보하고 있는 것으로 확인되고, ASMPT의 경우 SK 하이닉스의 HBM 공정에 활용되는 대부분의 die bonder를 공급하고 있는 것으로 확인됩니다.

리서치에 따르면 Di-D2W 장비를 개발하고 있고, 시장 상용화에 근접한 기업은 BESI, ASMPT, Shibaura 세 기업입니다.

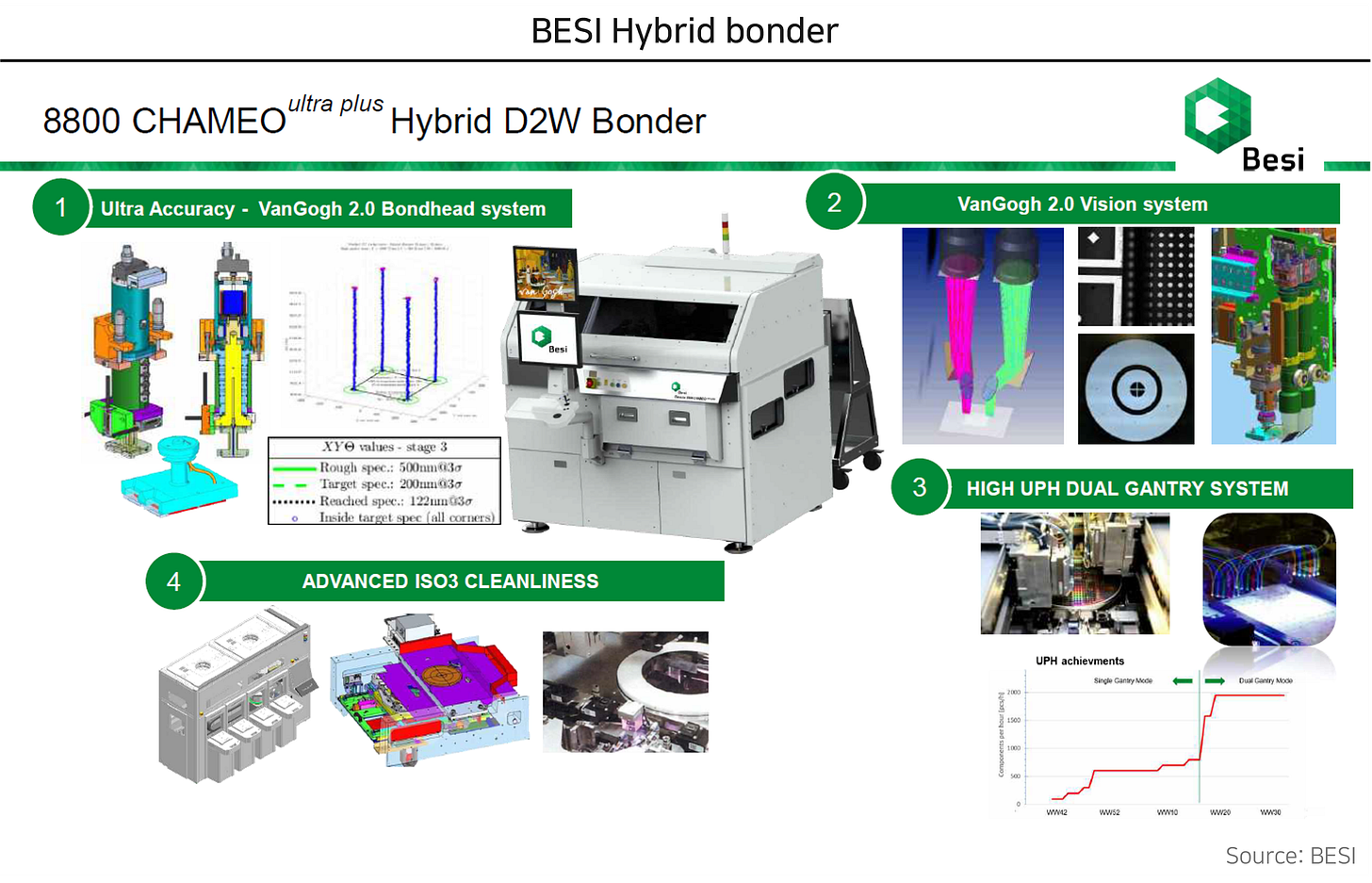

BESI

최초의 Di-D2W 상용화 장비 Datcon 8800 CHAMEO bonder를 개발하는데 성공했습니다. BESI에서 개발한 VanGogh Alignment 기술은 약 150nm의 정확도, 매 시간 ~2,000개의 bonding을 수행할 수 있다고 알려져 있습니다. 특히 2개의 Alignment arm을 하나의 장비 안에 배치해 공정 속도를 최대화할 수 있는 장비 구조를 만들었다는 점이 눈에 띕니다. 더하여 장비 자체에 클린룸 장비를 붙여 ISO class 3 수준의 환경을 구축합니다. 이는 앞서 언급했던 클린룸 장비에 대한 requirement를 충족합니다. 지금은 100nm 정확도를 위한 R&D를 지속해서 수행하고 있는 것으로 확인됩니다.

BESI는 2019년부터 Applied materials(AMAT)와 Hybrid turnkey 장비를 공동 개발하고 있습니다. AMAT은 HBI 형성 과정에 대한 공정 장비를, BESI는 Alignment/Bonding 장비를 개발하고 있으며, Wafer cleaning 공정은 함께 개발한 것으로 확인됩니다.

2024년 삼성에서 BESI와 AMAT의 장비를 기반으로 한 advanced packaging 설비 투자를 발표했습니다.

세계에서 처음으로 개발된 Hybrid bonding IP를 보유한 Adeia가 BESI의 장비를 활용해 7um의 pitch를 가지는 Di-D2W 공정을 개발했습니다. 참고로 Adeia는 DBI Ultra라는 브랜딩으로 Di-D2W에 대한 특허 라이선스를 보유하고 있으며, TSMC 다음으로 강력한 Hybrid bonding 특허 포트폴리오를 구축하고 있다고 평가받습니다. DBI Ultra에 대한 소개 영상도 함께 공유합니다.

현재까지의 HVM 도입 성과와 첨단 die bonding 장비에서 누적된 실적을 볼 때, BESI가 패키징 업계의 ASML이 되는 것을 조금은 기대하게 됩니다.

ASMPT

이에 질세라, ASMPT 역시 Lithobolt라는 이름으로 Di-D2W 장비를 공개합니다. ASMPT 제품은 200nm의 정확도, 매 시간 ~1,000개의 bonding을 수행할 수 있다고 발표했습니다. ASMPT 제품에는 alignment arm이 1개만 배치되어 있어 상대적으로 속도가 느립니다. 마찬가지로 ISO class 3 수준의 클린룸 장비도 함께 설치되어 있습니다.

ASMPT는 W2W hybrid bonding의 강자, EVG와 함께 Turnkey 장비를 개발하고 있습니다. 실제로 ‘23년 발표한 Lithobolt 제품 관련 논문에서는 ASMPT와 EVG의 연구원들이 공저자로 참여했습니다.

다음 세대 기술을 위해 IBM과 협업하고 있습니다. ‘23년 발표된 연구에서는 800nm의 pad, 4um의 patch를 가지는 hybrid bonding을 구현하였습니다.

BESI와 대적할 수 있는 강력한 경쟁자임이 분명합니다. 아직까지 주요 Foundry의 설비투자에 언급되지 않았지만, 하이닉스와의 관계를 생각하면 멀지 않은 미래 뉴스에 이름을 올릴 것이라고 전망됩니다.

이제는 점점 약팔이가 되어가는 것 같지만(?) BESI와 ASMPT는 마치 EUV 장비에서의 ASML과 Canon을 보고 있는 것 같습니다. 누가 ASML이 될지 계속해서 가늠해야겠지만, 앞서 언급한대로 Bonding 장비의 Q 증가 현상을 목도했으므로, 두 자산에 동시 투자하는 것도 꽤나 괜찮은 접근이 될 것이라고 생각합니다. (반도체 산업에 베팅하는 리스크 만땅 투자..)

Shibaura

Shibaura는 TSMC에 R&D용 파일럿 장비를 제공하고 있는 것으로 알려져 있습니다. Pure player도 아니고, BESI/ASMPT와 달리 HBI 형성 공정에서의 파트너를 확보한 것이 아니기 때문에 아직은 Di-D2W 시장에서 어느 정도의 지배력을 가지게 될지 모르겠습니다. 하지만 무려 “TSMC”에 공급한 이력이 있는 만큼 꾸준히 현황을 확인해볼 필요가 있을 것 같습니다.

우리나라 한미반도체, SEMES의 경우 아직까지 현 세대 TC Bonder 기술에서도 뒤따라가고 있는 모양새입니다. 이에 따라 시장 초기 Hybrid bonding 장비에서의 경쟁력은 기대하기 어려워 보입니다.

정리: Key Momentum & Limitation & Supply chain landscape

현황

Di-D2W를 기반으로 High volume manufacturing(HVM)에 성공한 사례는 아직까지 발표되지 않았습니다. 하지만 HVM에 적합한 수준의 장비가 공급되기 시작했고 구매자가 삼성이라는 사실을 상기할 때, 머지않아 Di-D2W 시대가 개화할 것이라고 생각합니다.

향후 시장 확장성

Key momentum = HBM (가제: 삼성, “이 카드에 모든 걸 걸겠어”)

Logic 3D integration 과정에서 새로운 IP 생태계가 구축되어야 합니다. 위-아래로 Logic을 연결해본 전례가 없기 때문입니다.

따라서 3D stack이 일상화된 HBM에서 우선적으로 Di-D2W가 적용될 것입니다. 핵심 장점은 다른 무엇보다도 ‘Bandwidth가 100배 넓어진다’는 점입니다. HBM에서 Banwidth 말고 더 중요한 기술이 있을까요? 삼성, 하이닉스, 마이크론으로 좁혀져 있는 HBM 생태계에서 유의한 격차는 분명 Di-D2W 기술에서 만들어질 것이라고 생각합니다.

HBM 기업들은 Di-D2W 기반의 HBM 적층 기술을 확보하고, W2W 기반의 3D DRAM (DDR6+) 기술을 확보해야 합니다. 특히나 HBM이 GPU 내부로 Integration되면서 독립적인 DRAM의 시장 점유율은 감소할 것이 확정적입니다. 다르게 이야기해 DRAM 시장 전체에서 HBM의 비중은 지속적으로 높아질 것이 분명합니다. 따라서 위 두 가지 기술을 중심으로 경쟁력을 확보하는 것은 ‘사활’이 달린 일입니다.

일석이조라고, HBM을 통해 다층 Hybrid bonding 역량을 증명하게 되면 Foundry 측면에서의 영업력도 강화됩니다. Logic은 메모리와 달리 수직 방향의 연결 경험이 없기에 HBM처럼 수십 층을 쌓지는 못할 가능성이 높습니다. 초기에 2-layer를 위한 IP가 개발되면서 Co-D2W 도입이 우선적으로 진행될 것이라고 생각합니다. AMD와 TSMC의 합작품 V-cache가 대표적인 예시입니다. 하지만 그 다음 세대에는 Logic도 Multi-layer로 확장할 것이고, Memory와 융합하며 Process-in-Memory로 전환되어야만 합니다. 따라서 궁극적으로는 Di-D2W 기술이 도입될 것이고, HBM을 통해 수십 층 쌓아낼 줄 알던 기업들에게 Foundry 영업력이 생기는 것은 꽤나 자명해 보입니다.

결론적으로 우리나라의 삼성, 하이닉스는 Hybrid bonding을 성공시켜야만 하는 입장에 놓여 있습니다. 어려워도 해내야 합니다. (라고 믿으며 주식을 사는….것..이죠) 시장 개화가 머지않았다고 판단하며, 이에 따라 궁극적인 기술 Di-D2W value chain 전반에 유의한 투자 기회가 있다고 생각합니다.

Overall Landscape & Conclusion

Hybrid bonding은 기존 패키징 공정과 완전히 다른 성격을 띄기 때문에, 시장 개화에 따라 주요 장비/부품에 대한 수요가 증가할 것으로 전망됩니다.

폭발적인 시장 개화를 이끌어내기 위해서는 Target die 시장이 넓어야 하며, 현재 가장 뜨거운 감자인 HBM에서 기술적 변혁을 이끌어낼 수 있는 Di-D2W 장비 기업에게 큰 투자 기회가 있을 것이라고 생각합니다. 이에 따라 BESI, ASMPT 두 기업을 전체 시장 leader로 설정합니다.

모든 Value chain에서 전반적인 수요 증가 흐름을 맞이합니다. 이들 중, Hybrid bonding이 전체 성장의 중요 부분을 차지하는 value chain은 Plasma dicing 장비와 유관 부품 (RIE 강도로 인한 교체 주기 감소), 세척 장비로 추려질 것이라고 생각합니다. 반도체 FEOL/BEOL, 패키징 공정 모두에서 그닥 활용되지 않다가, Hybrid bonding 구현에 꼭 필요해지는 영역이기 때문입니다.

Hybrid bonding 과정에서 가장 많이 언급되는 것이 바로 “플라즈마”입니다. PECVD, Plasma dicing, Plasma activation 세 공정에서 모두 필요한 부품에서 가장 많은 Q 증가를 기대할 수 있습니다. 저의 지식 선에서 떠올린 것은 플라즈마 생성기입니다. 플라즈마는 기존 반도체 패키징에서 전혀 활용되지 않았기 때문에 아직까지 크게 조명받지 않고 있어 매력적인 valuation을 유지하고 있습니다. (뉴파워플라즈마는 횡령/배임 이슈, 도우인시스 인수 건 등 대외적인 잡음이 많아 조금 더 살펴보아야 합니다.) 기술적 해자를 지닌 기업을 찾는다면 Hybrid bonding 시장 개화와 함께 유의한 실적 변화를 기대해볼 수 있겠습니다.

IP Troll Adeia의 포트폴리오가 생각보다 강력합니다. W2W 기술인 DBI, Di-D2W 기술인 DBI Ultra로 나뉘는데요. 단순히 아이디어만 내는 것이 아니라 실제 공정까지 논문으로 출판하고 있으며, 어떤 장비를 활용했는지도 강조하고 있습니다. 개인적으로 가장 눈여겨 본 부분은 하이닉스의 DBI Ultra 라이선스 계약입니다. 아직까지 HBM 시장에서 Hybrid bonding을 활용하지 않기 때문에 조명받고 있지 않지만, 하이닉스가 Hybrid bonding을 HBM에 적용하면 최대 수혜를 받는 기업이 될 수 있습니다. 지금 당장도 나쁘지 않은 Cash cow를 보유하고 있어 하방을 유지한 채로 Hybrid bonding의 upside를 노려볼 수 있다는 판단입니다.

마지막으로, 이번 포스팅에서 다루지 않은 ‘검사장비’에 대한 언급이 필요합니다. 관련해서 짧은 시일 내에 업데이트 해보도록 하겠습니다.

모두 긴 글 읽어주셔서 감사합니다. 즐겁게 읽으셨다면 좋아요… 구독… 여기저기 공유… 부탁 드립니다.